凭借1英寸大型目标CMOS传感器的星光成像能力,该机器支持更宽的照度范围的超高清成像应用。同时提供两种补光方案,满足全天候监控的需要。一是通过集成设计LED频闪灯补光,在没有外部补光的情况下,轻松实现全天候车辆捕捉和车牌识别;二种是使用外置闪光灯来补光,此时,车内外的信息都可以得到充分的呈现。

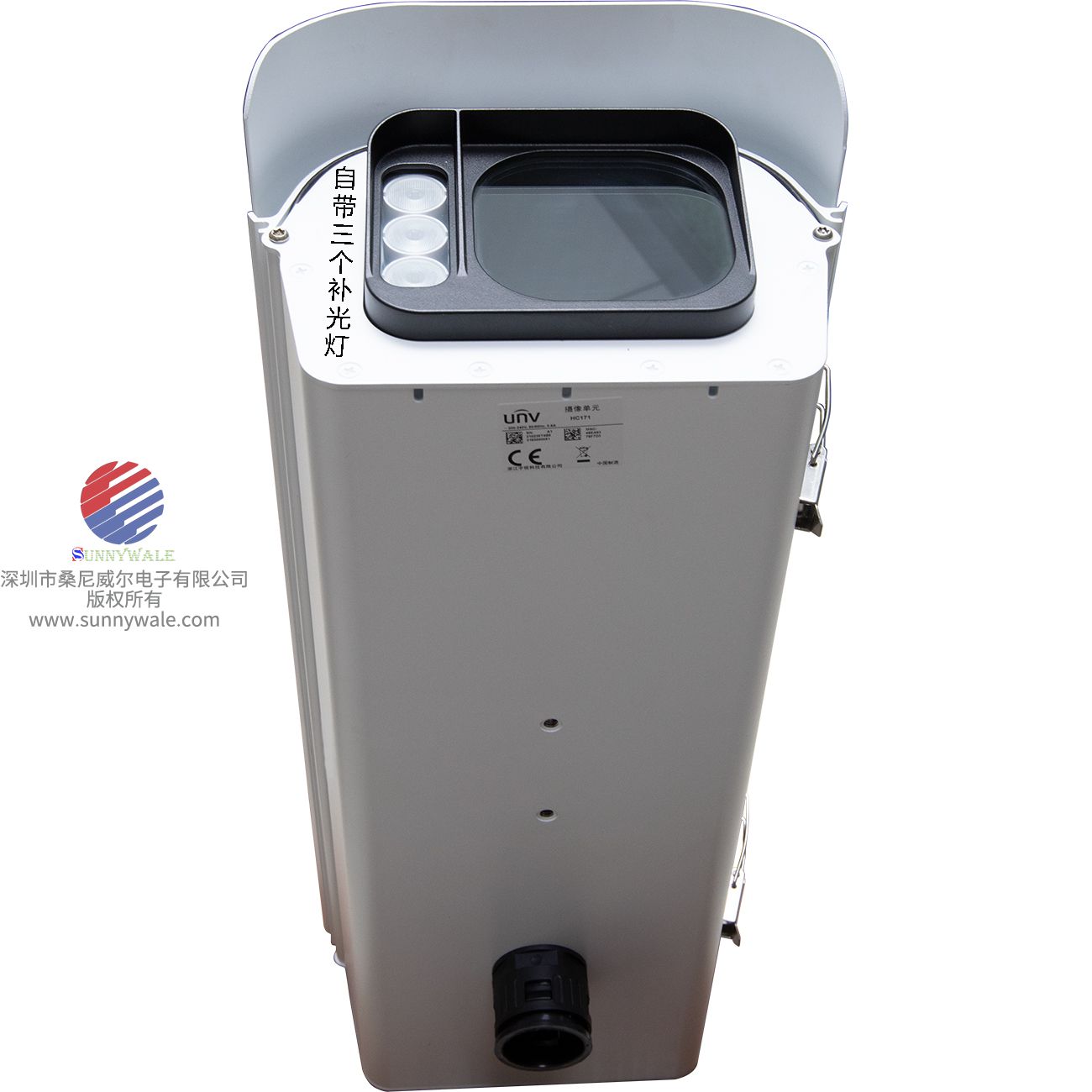

该盾牌自带集成补光灯,仅道路环境照明30Lux,还能保证稳定的车牌识别率,清晰的车身颜色。

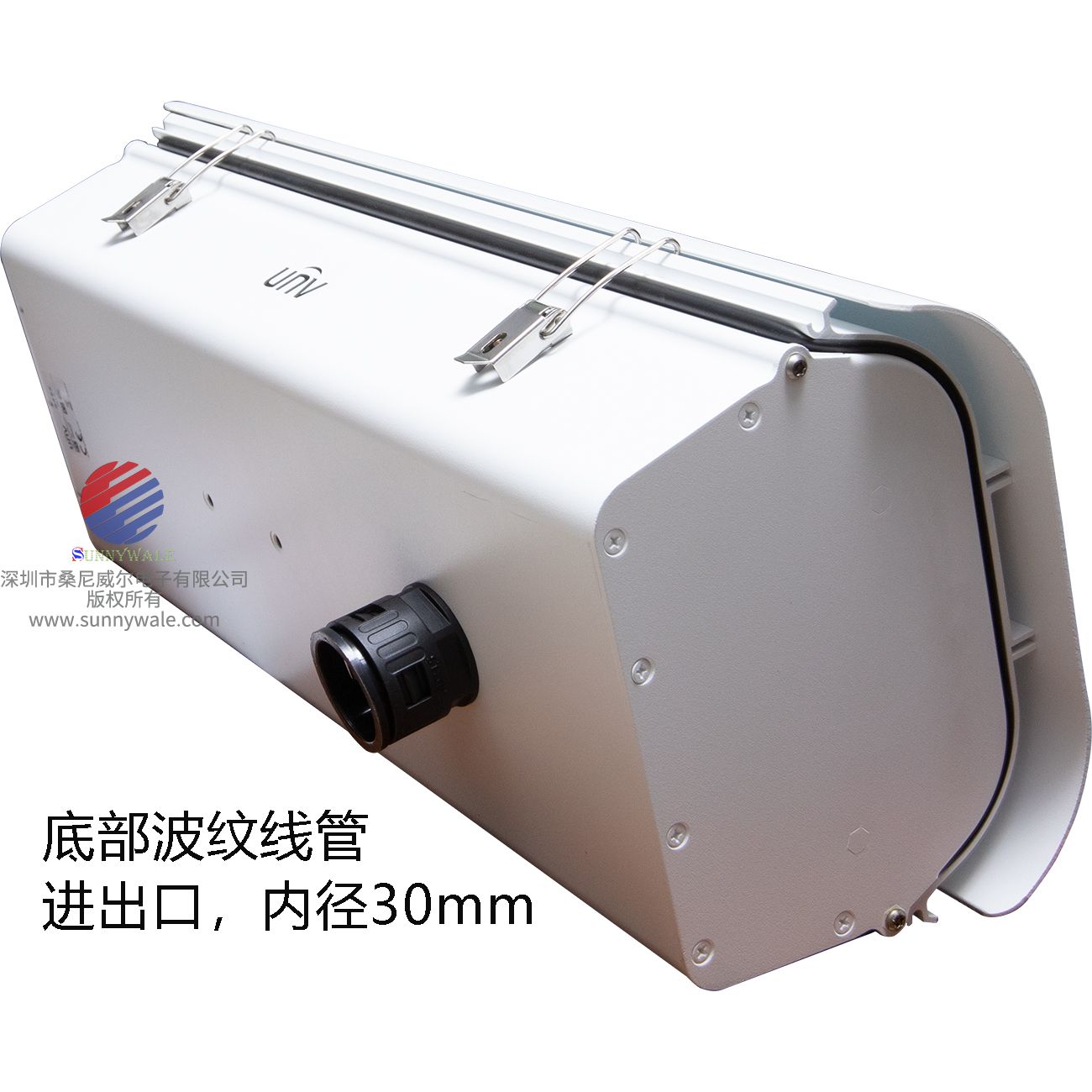

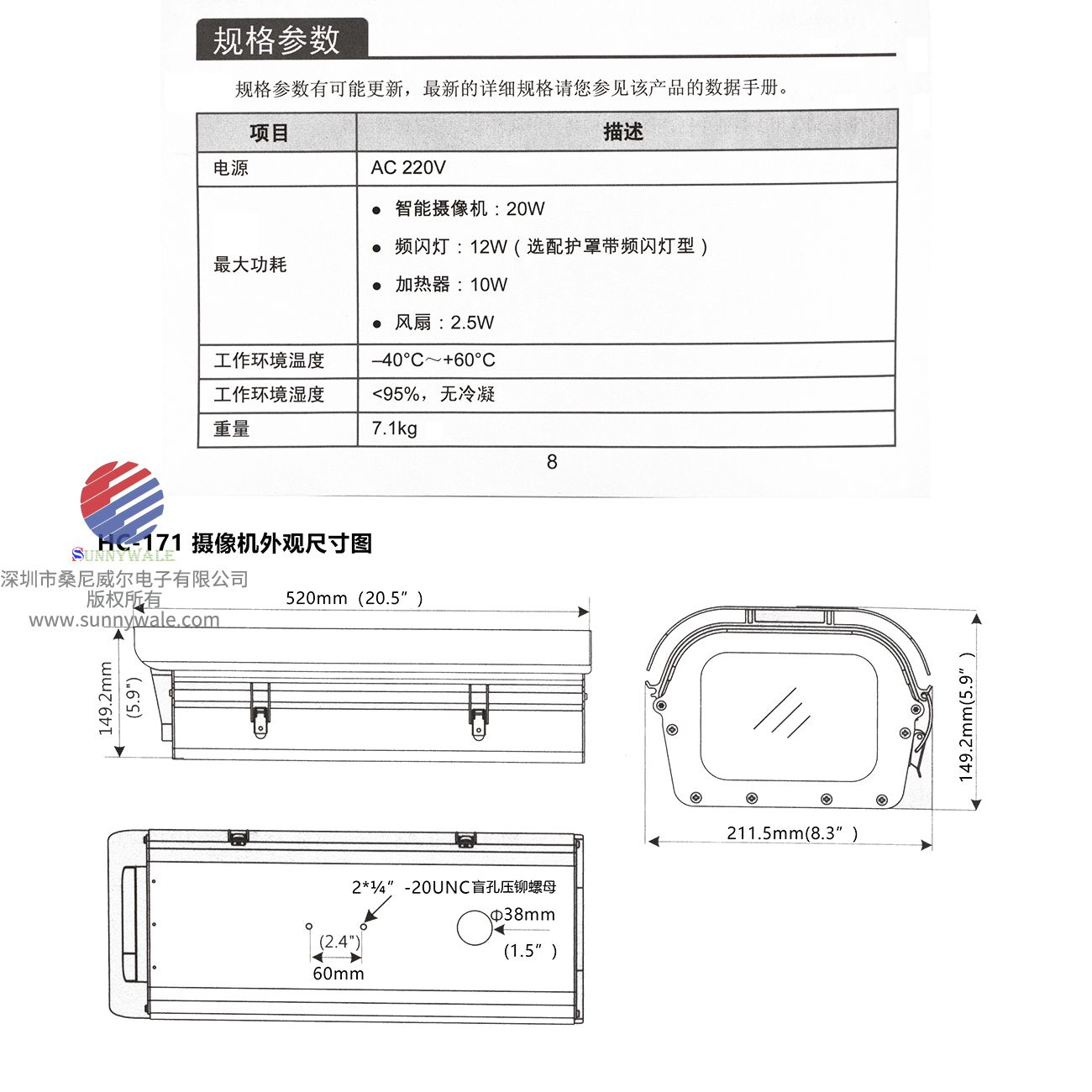

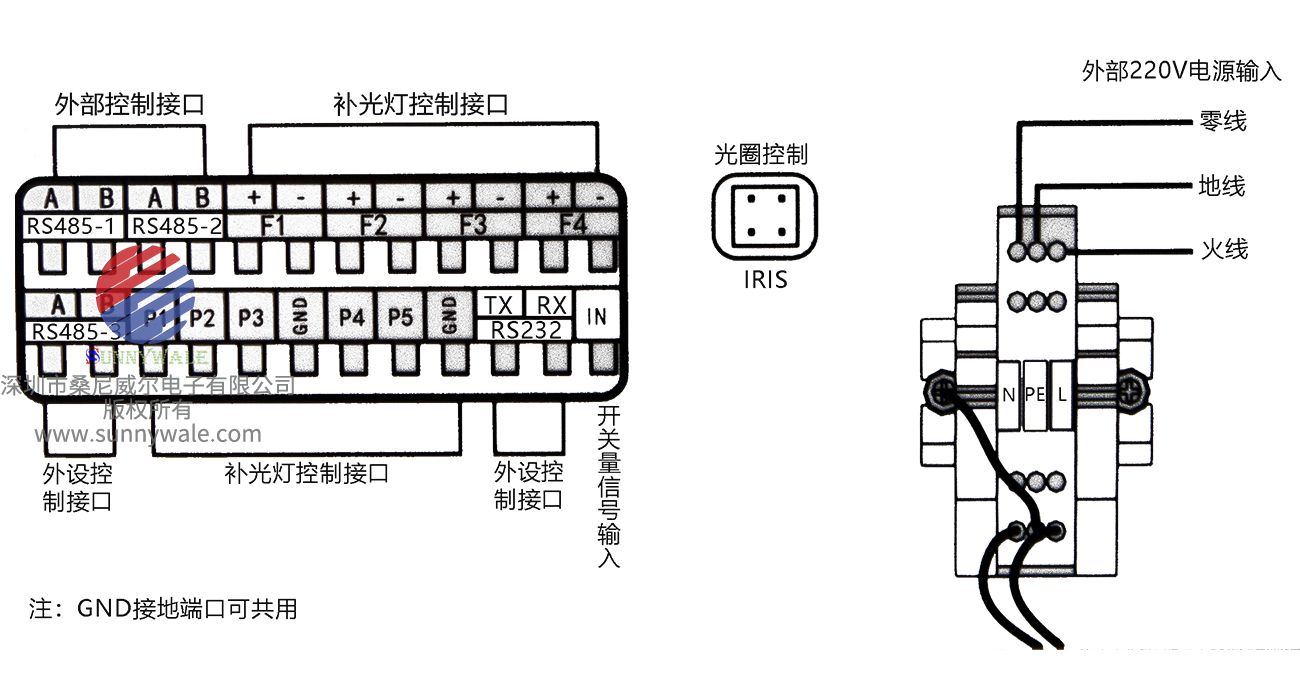

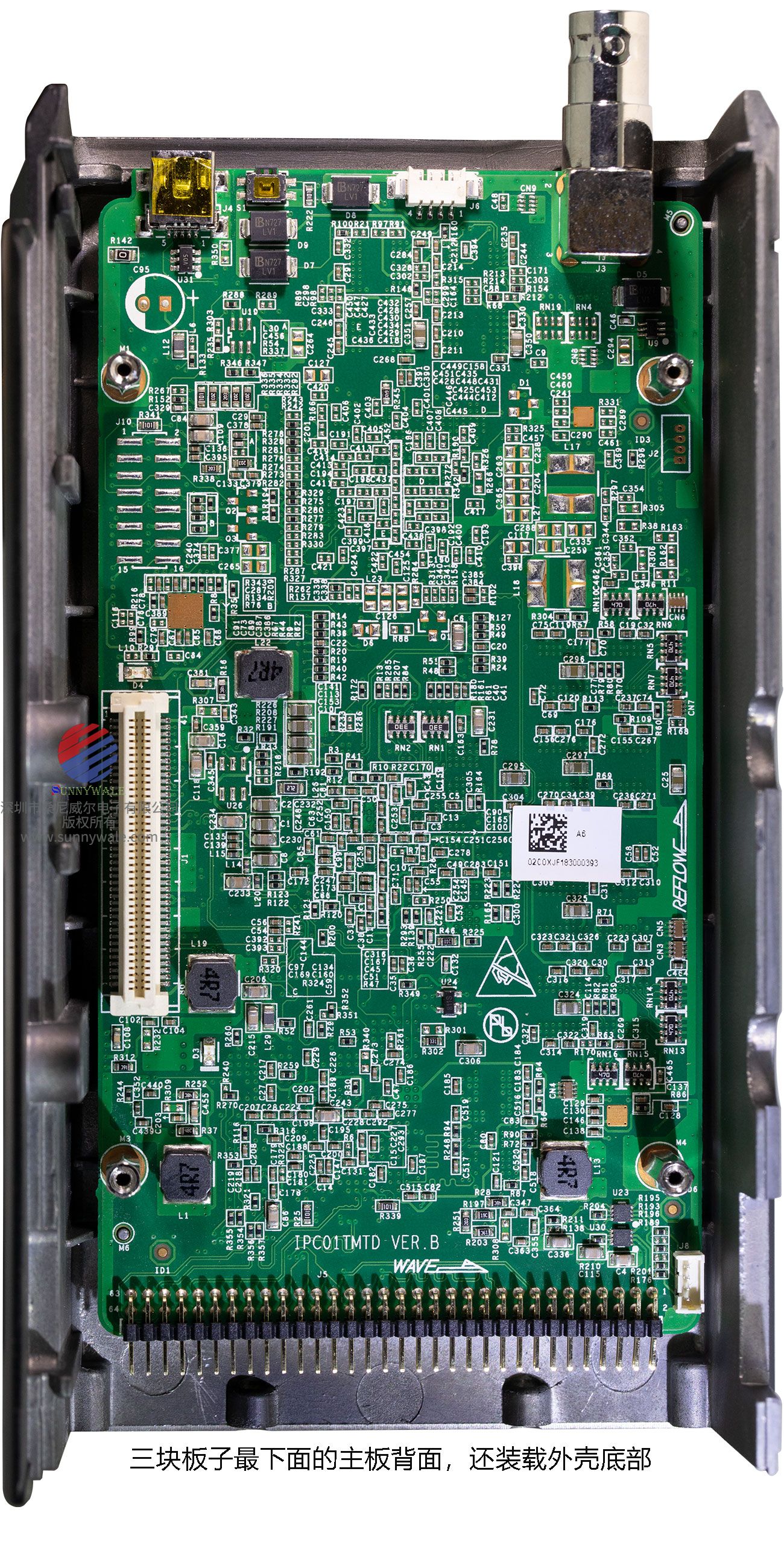

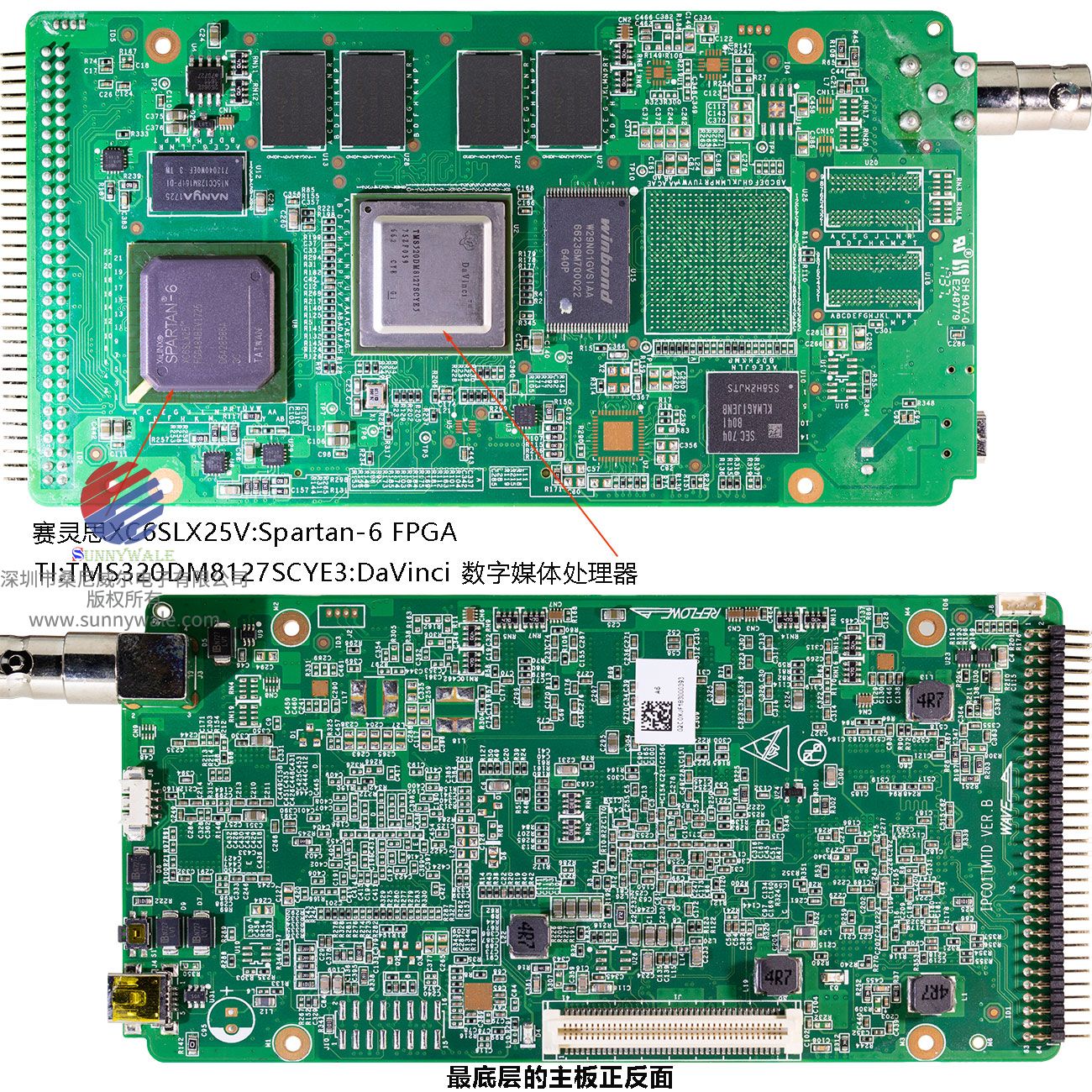

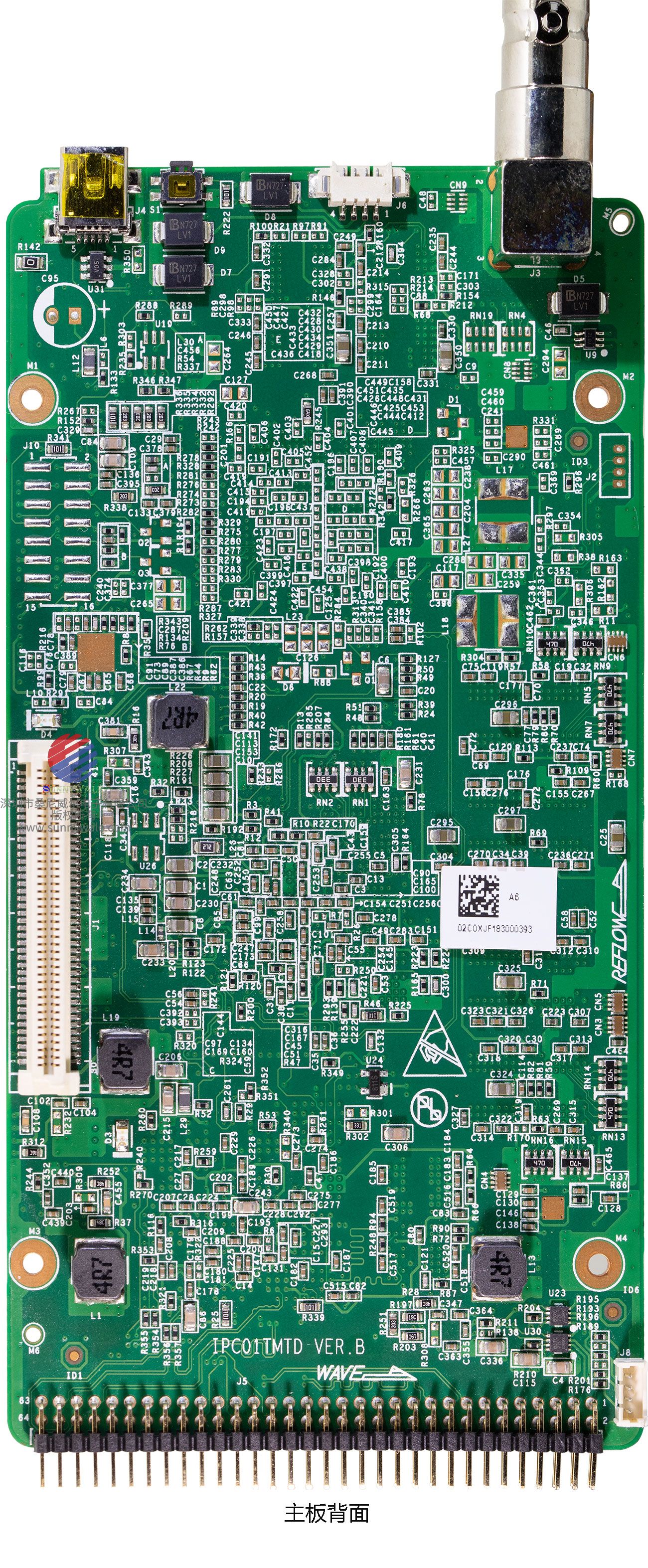

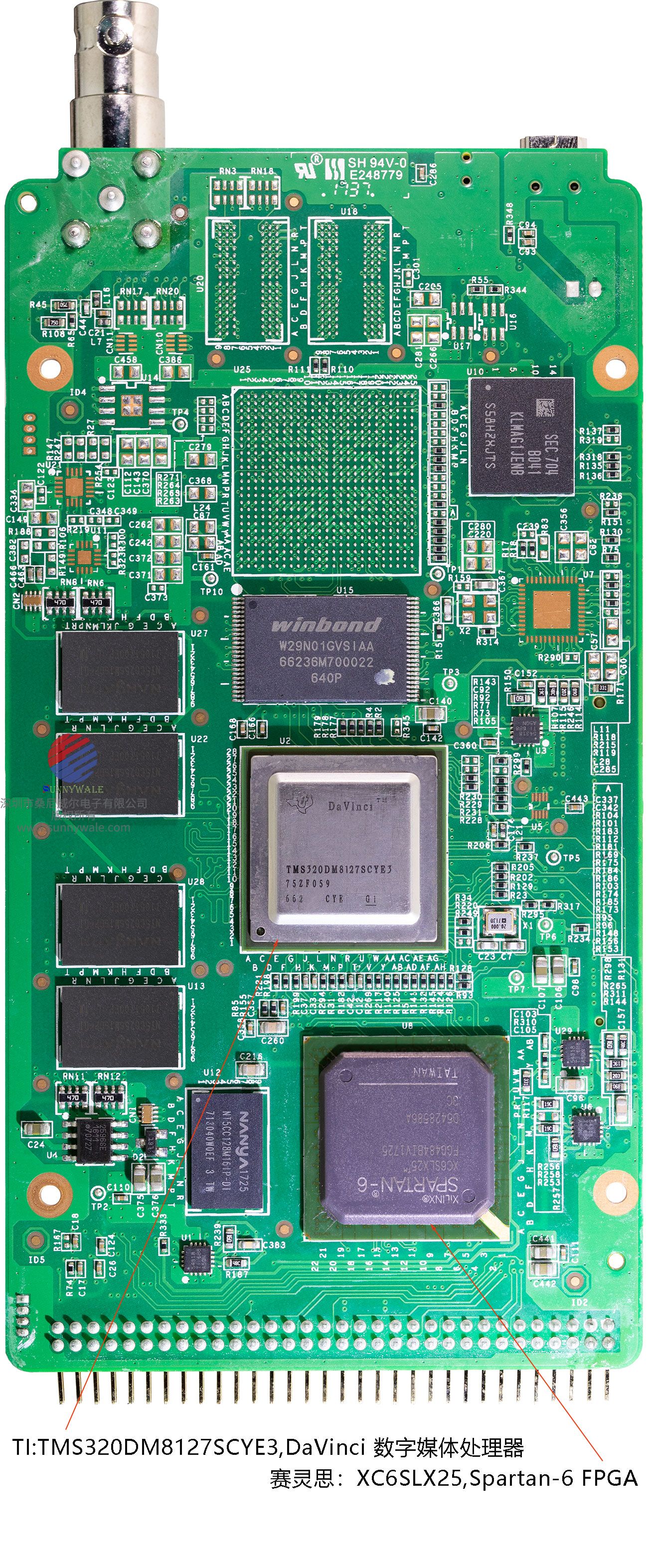

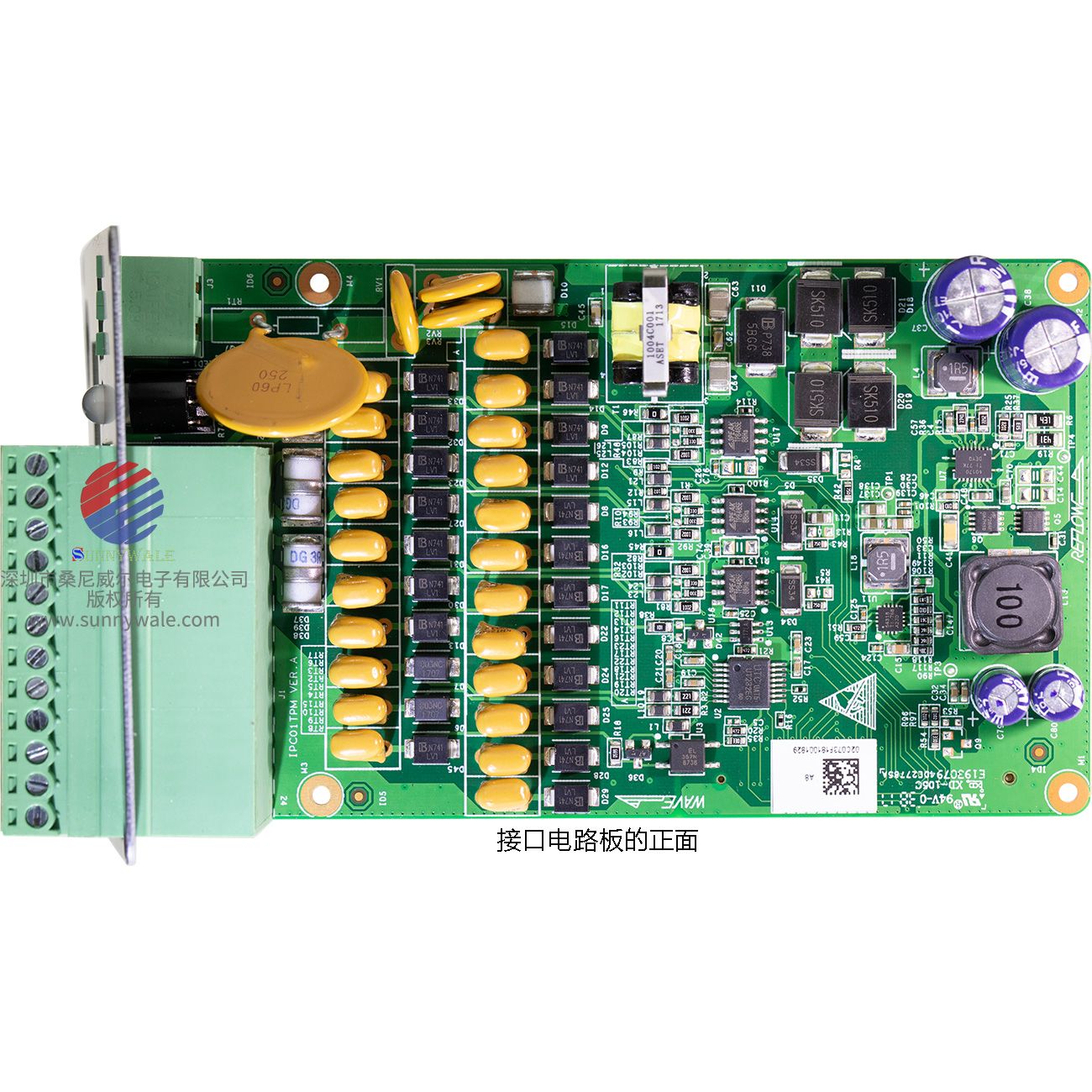

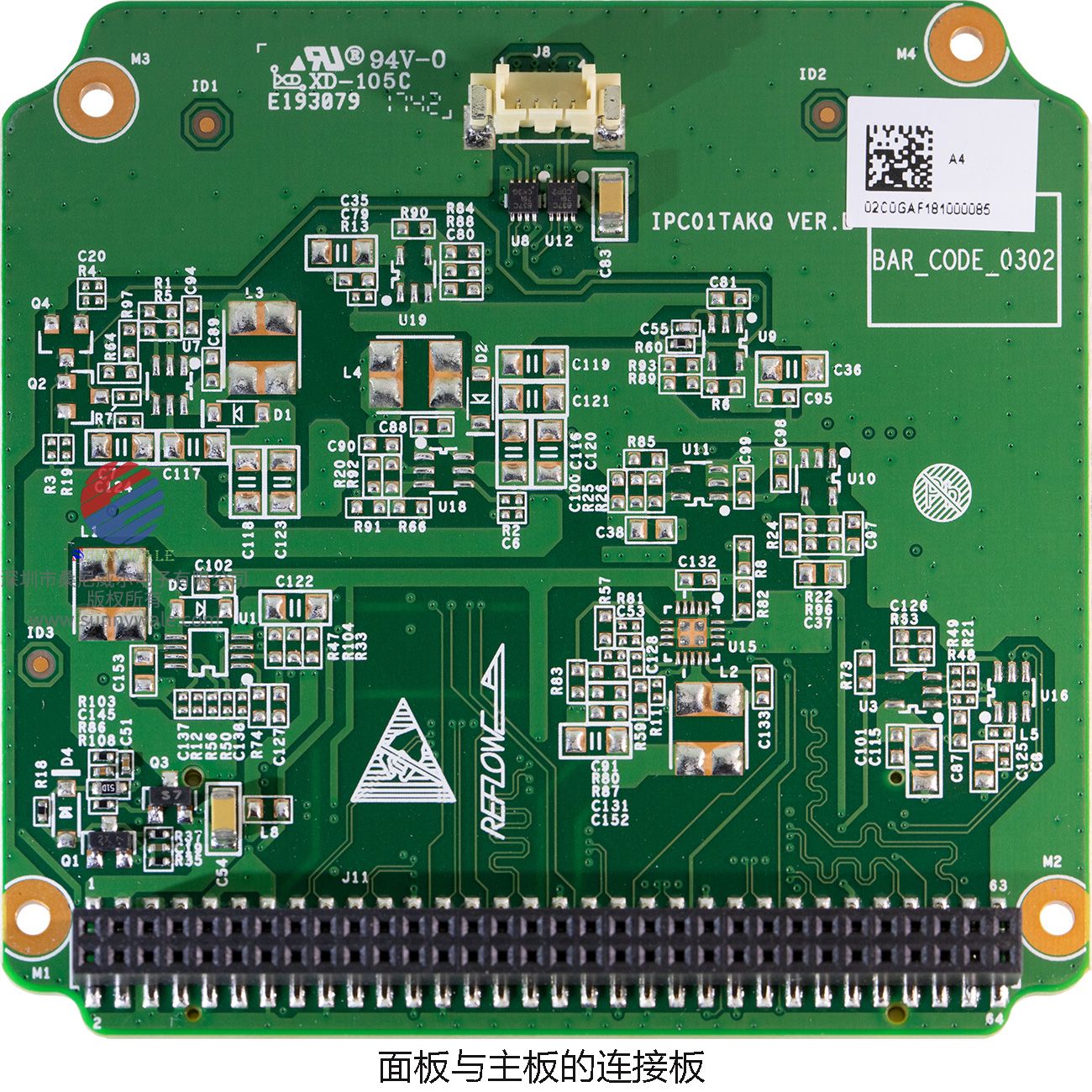

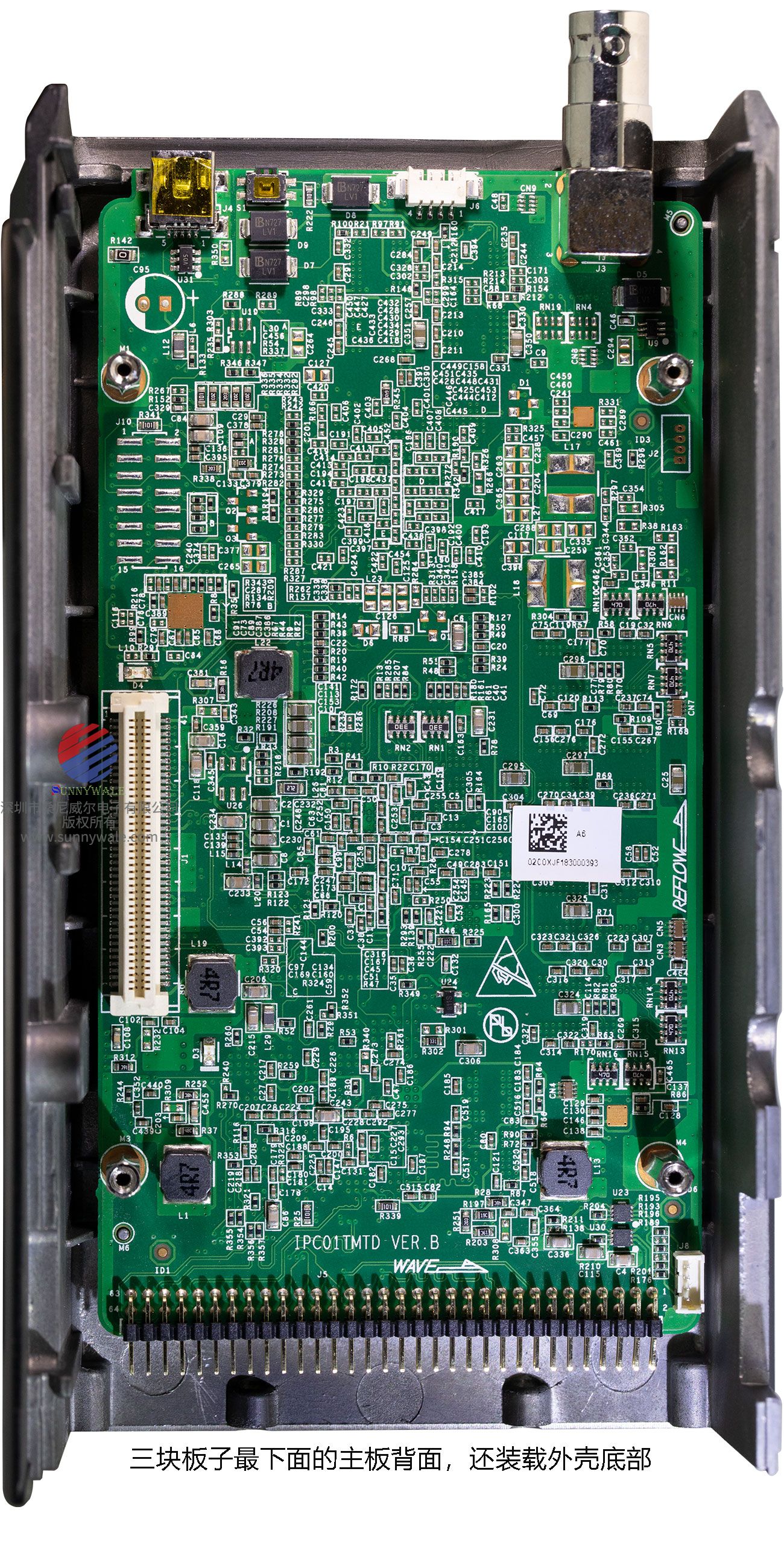

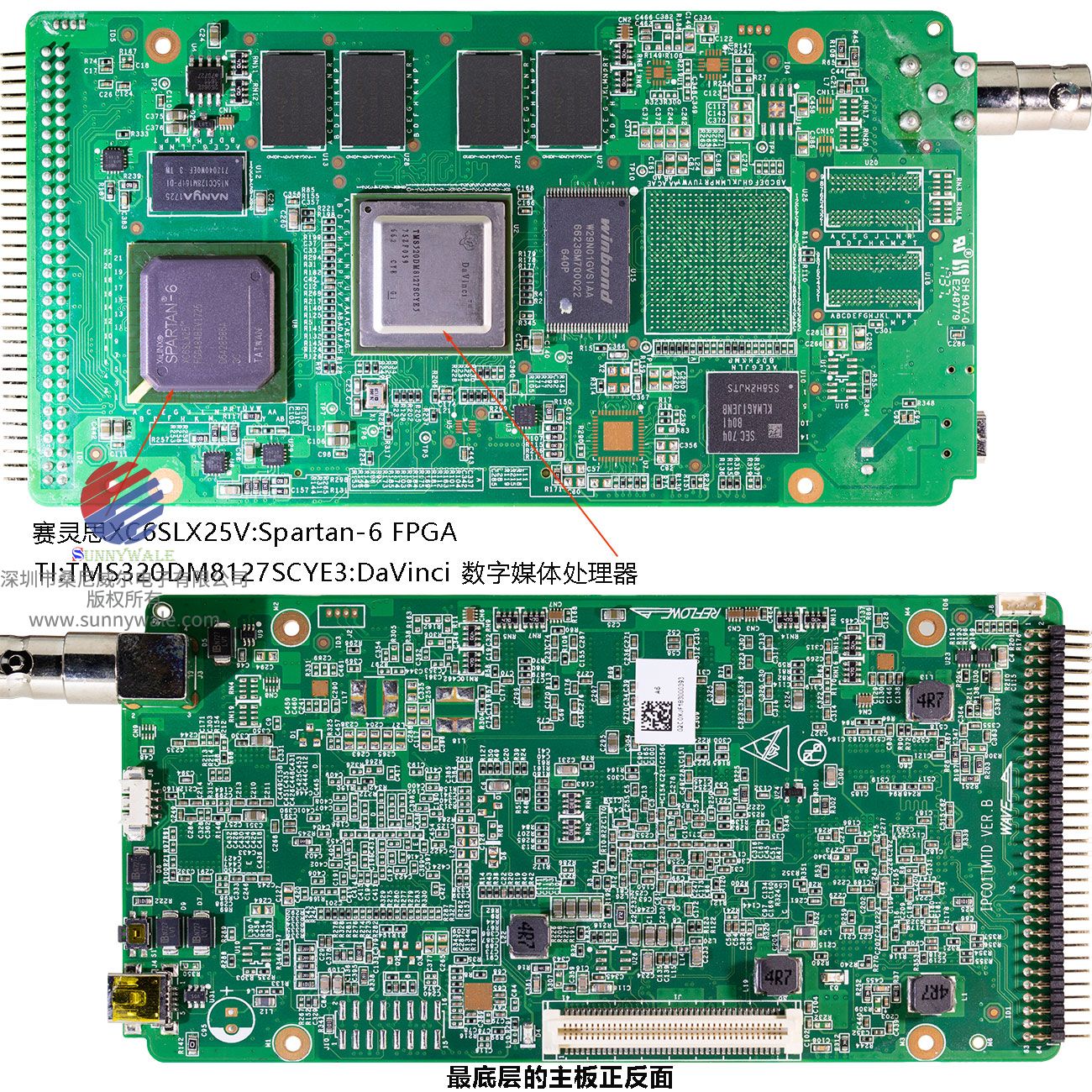

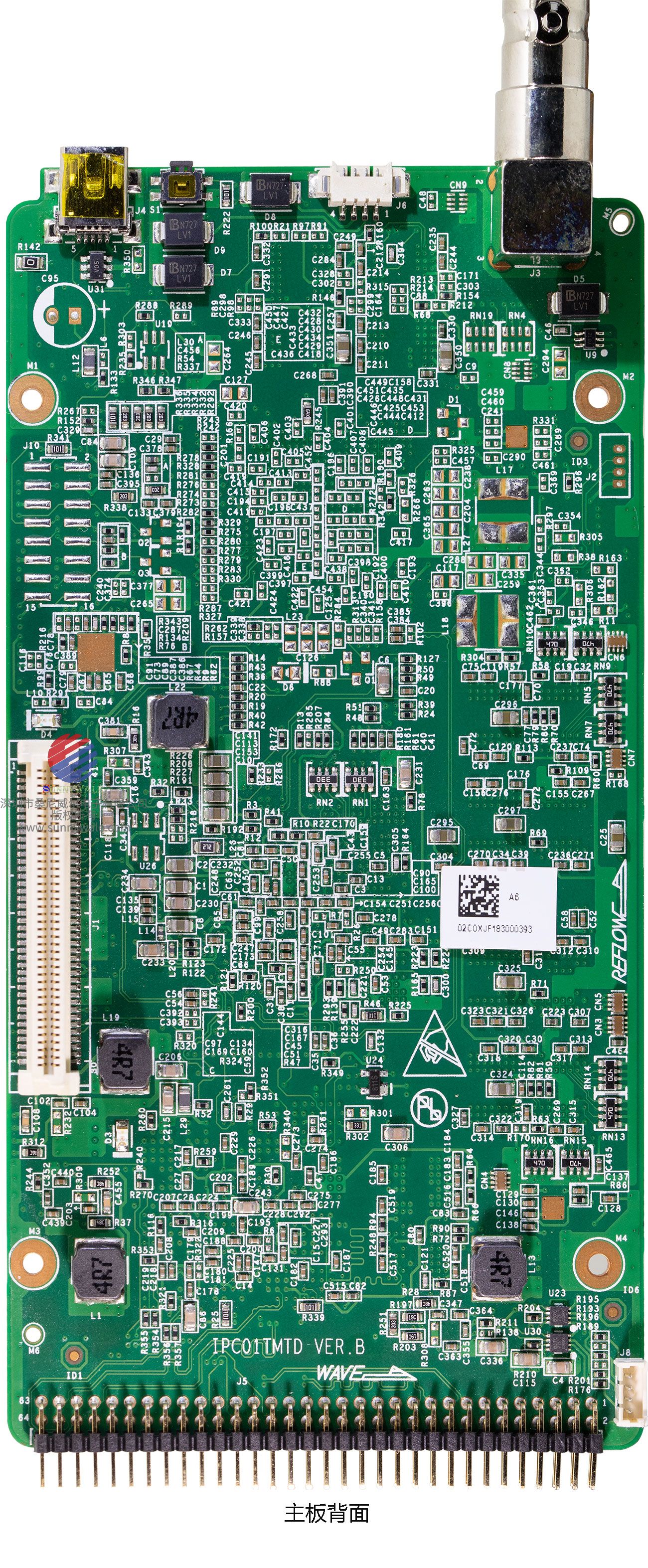

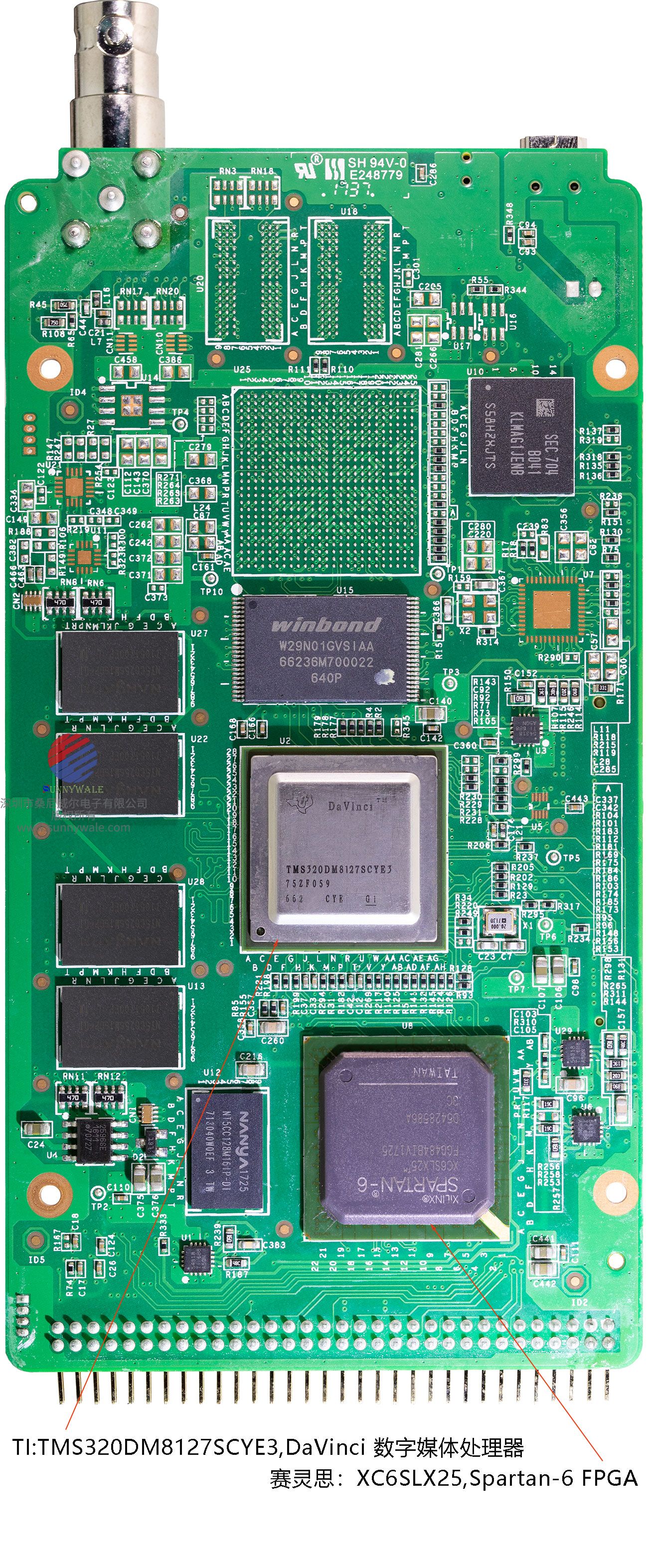

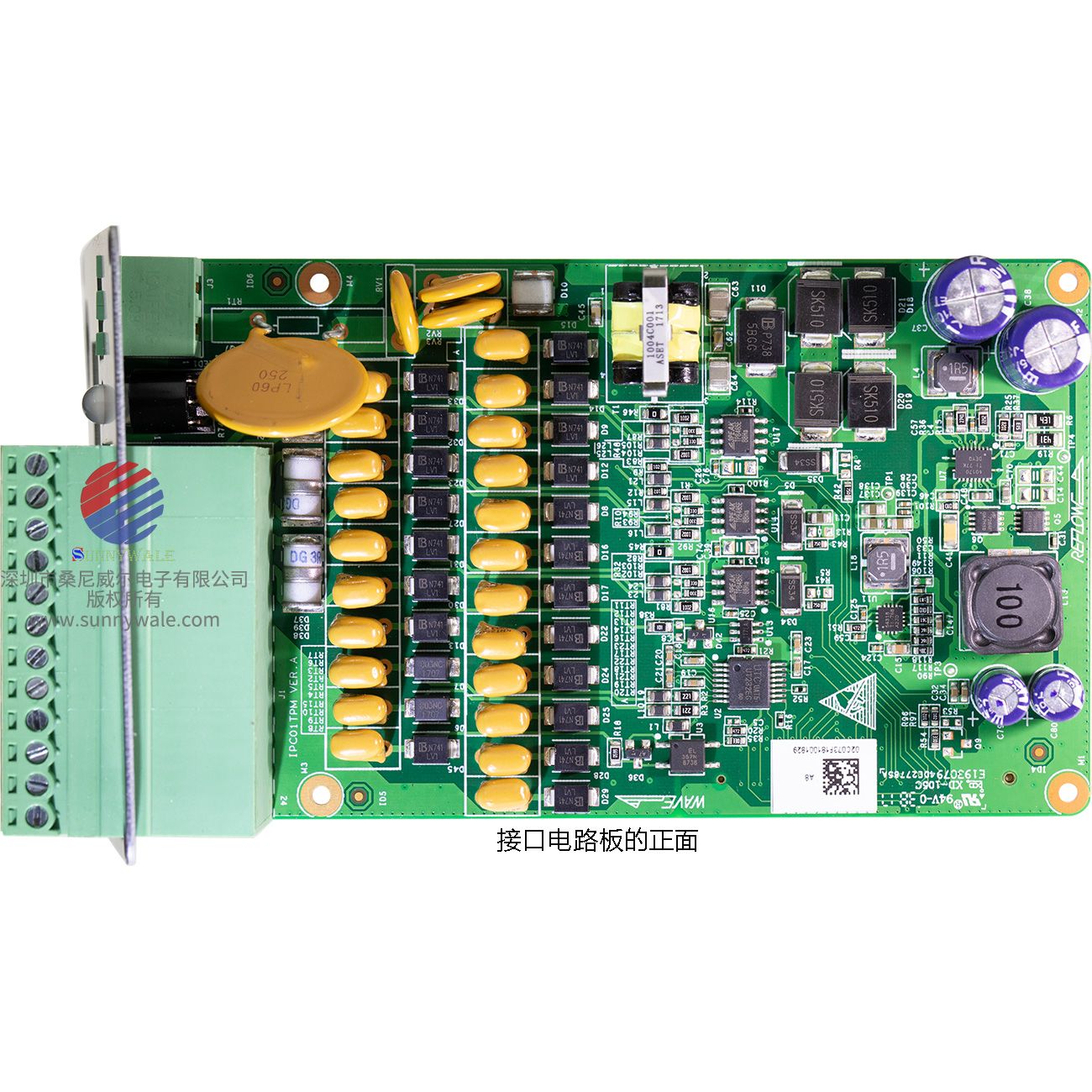

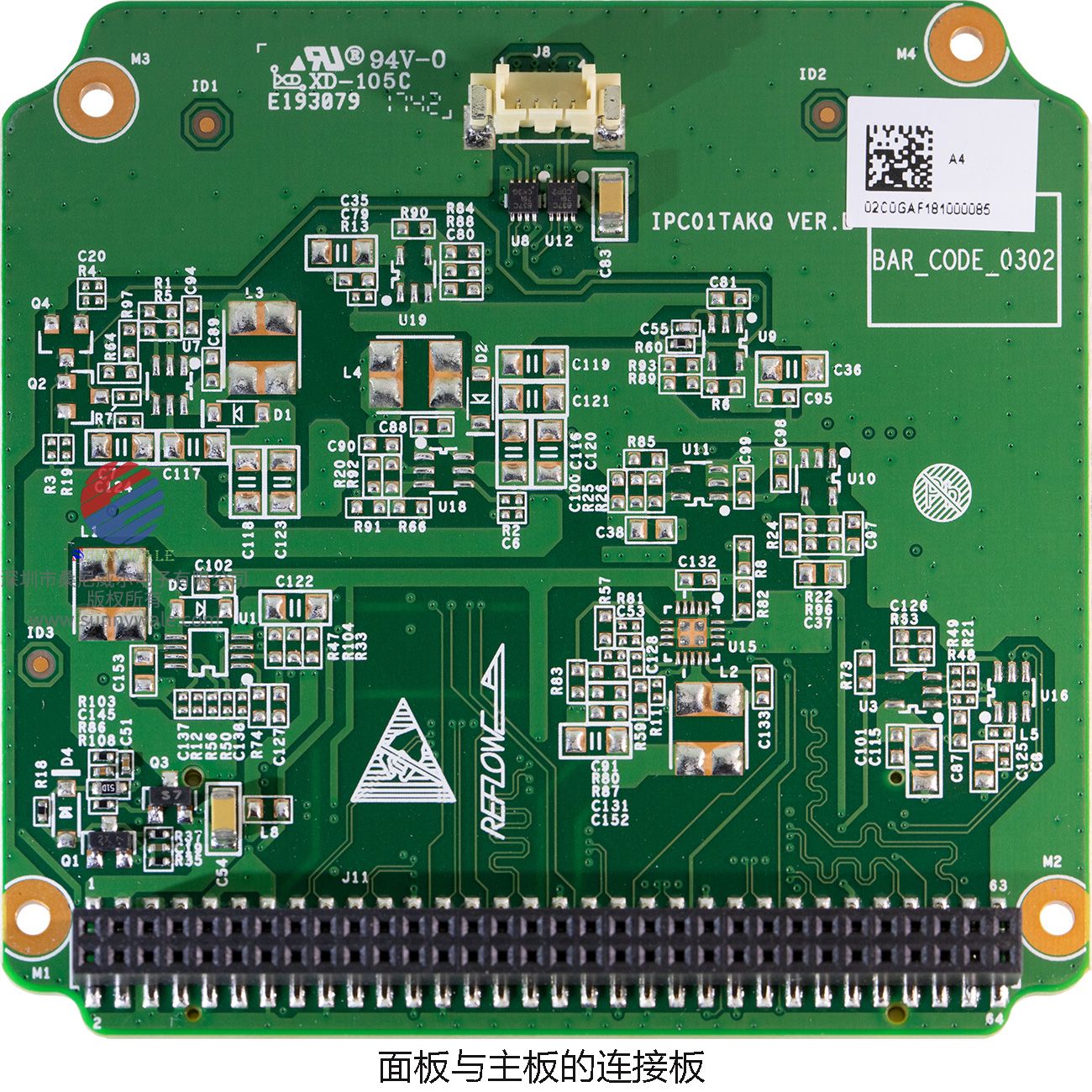

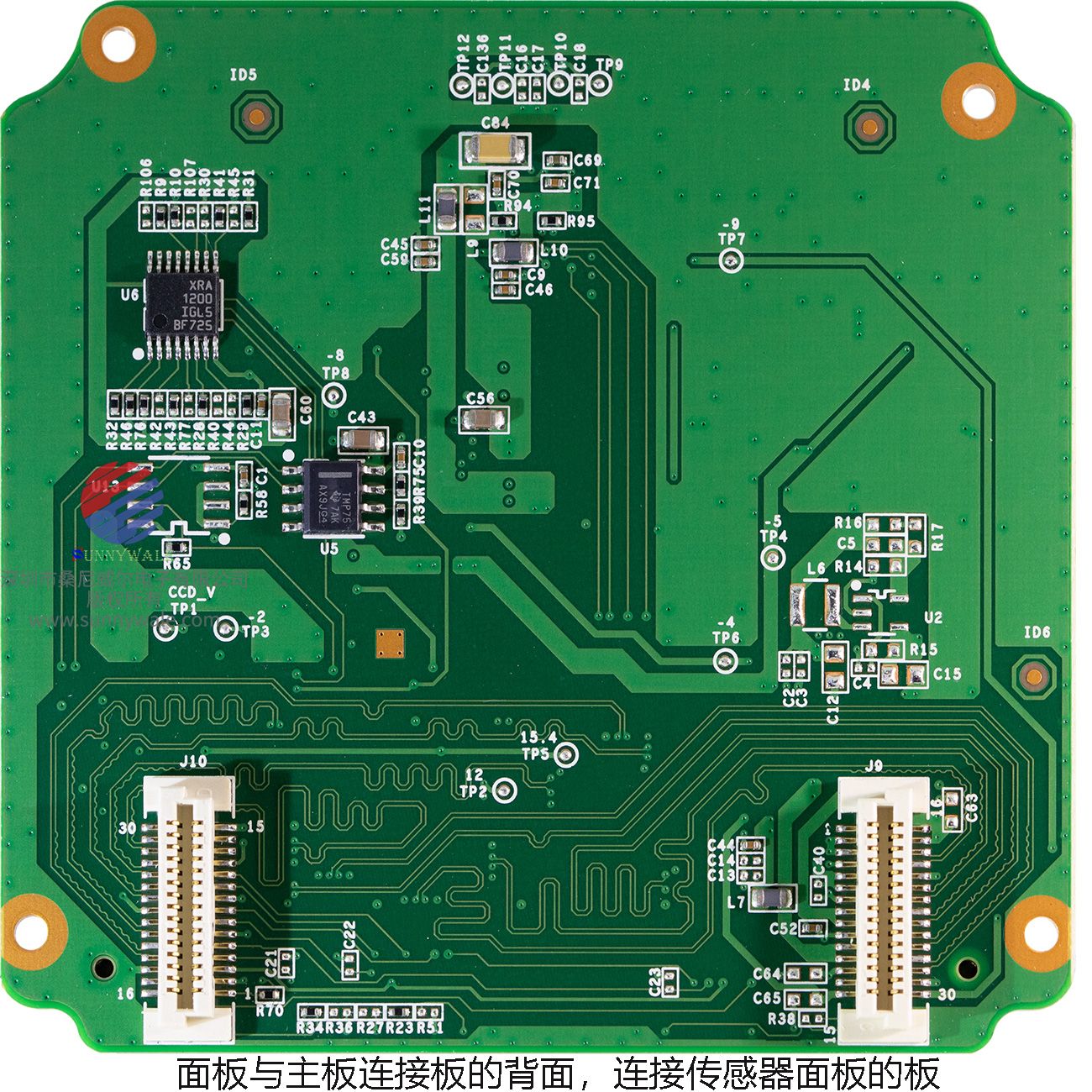

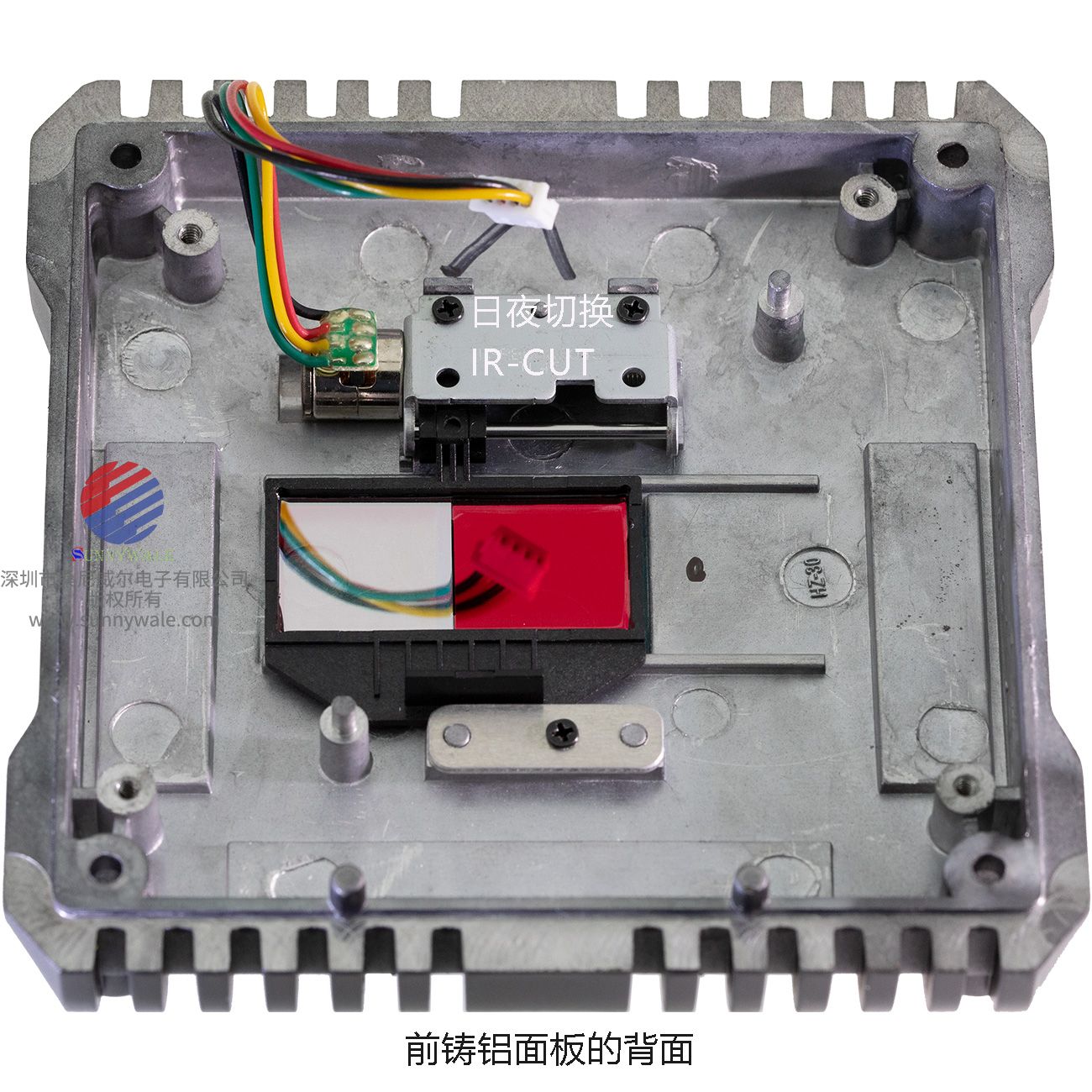

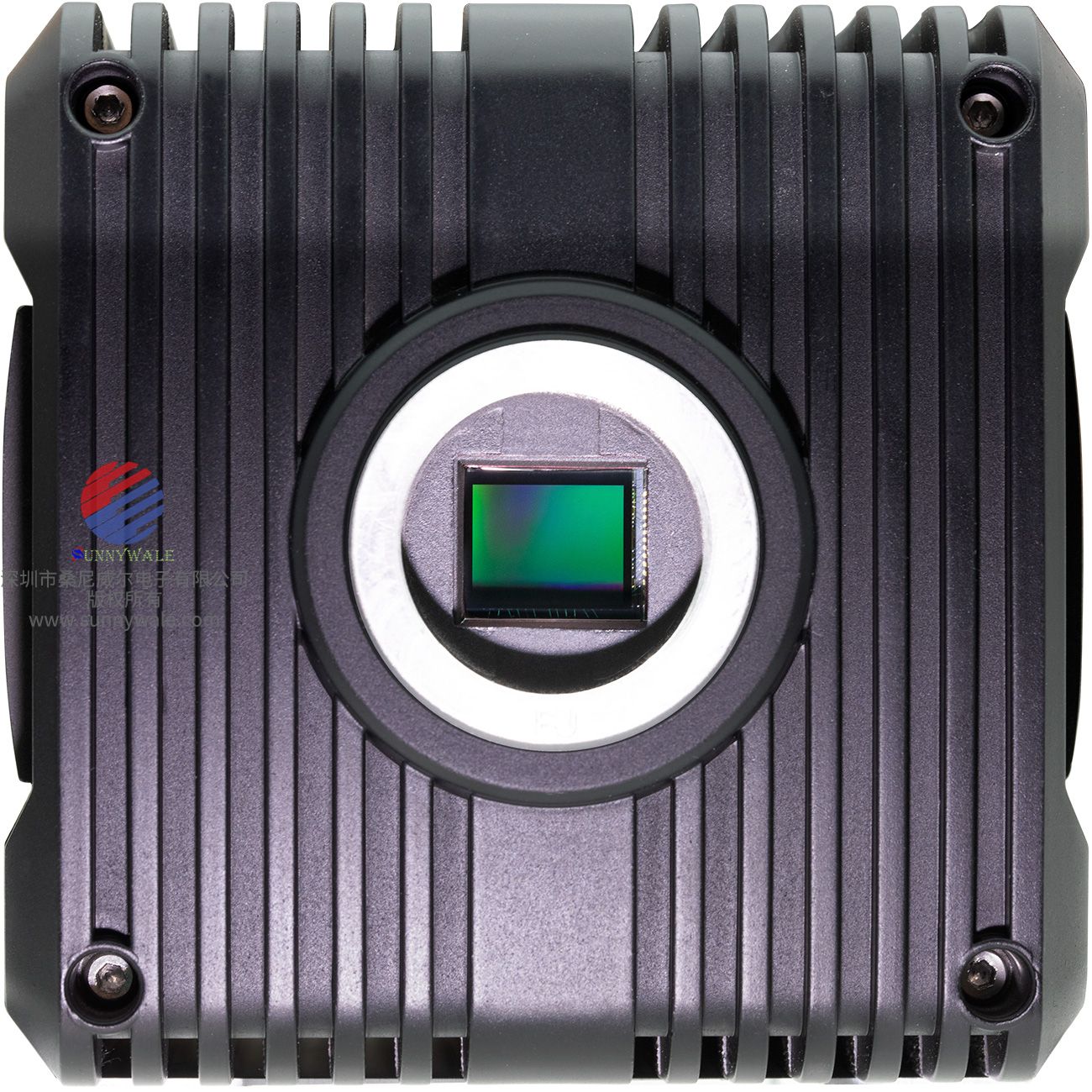

以下宇视HC171摄像机拆解详情:

以下宇视HC171摄像机拆解详情:

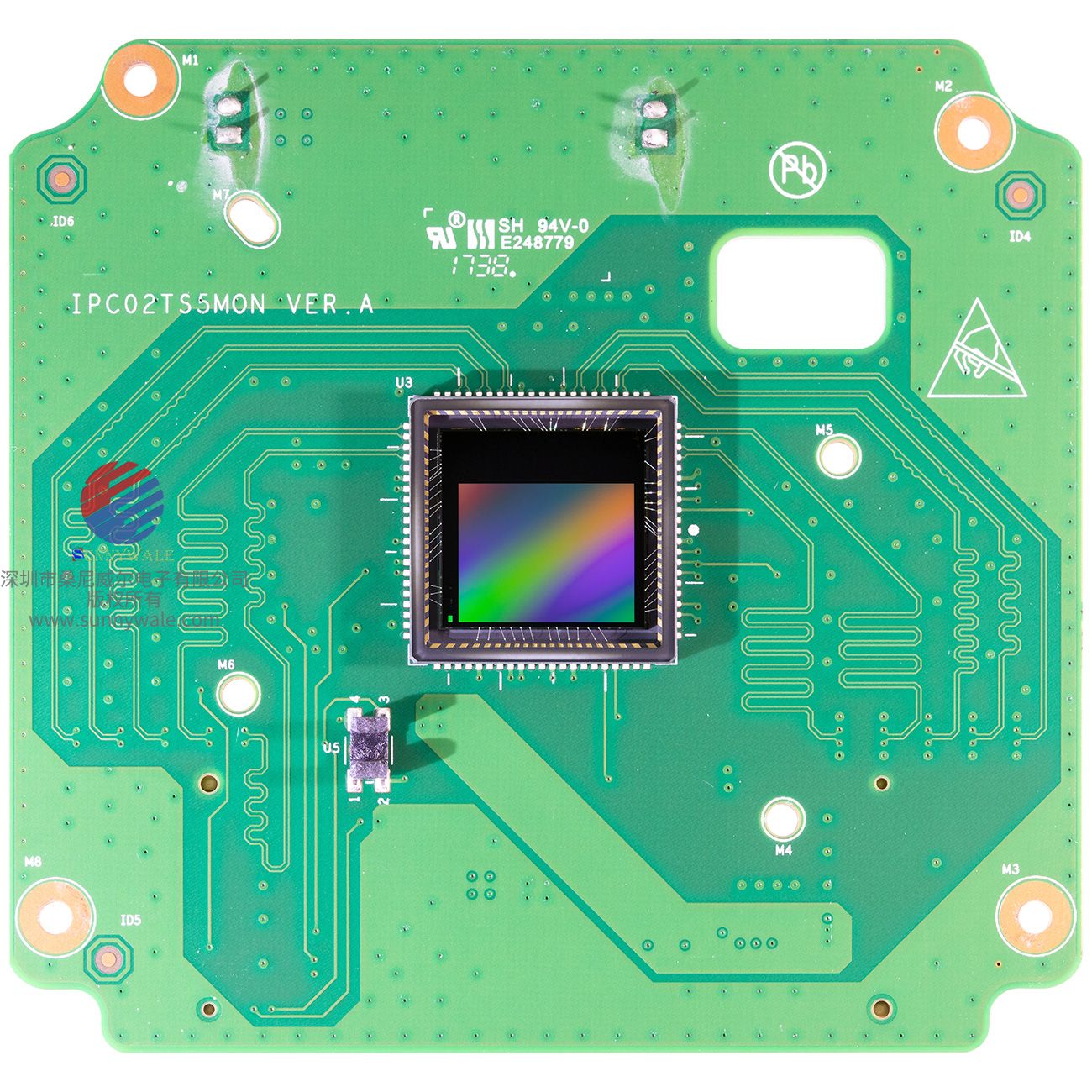

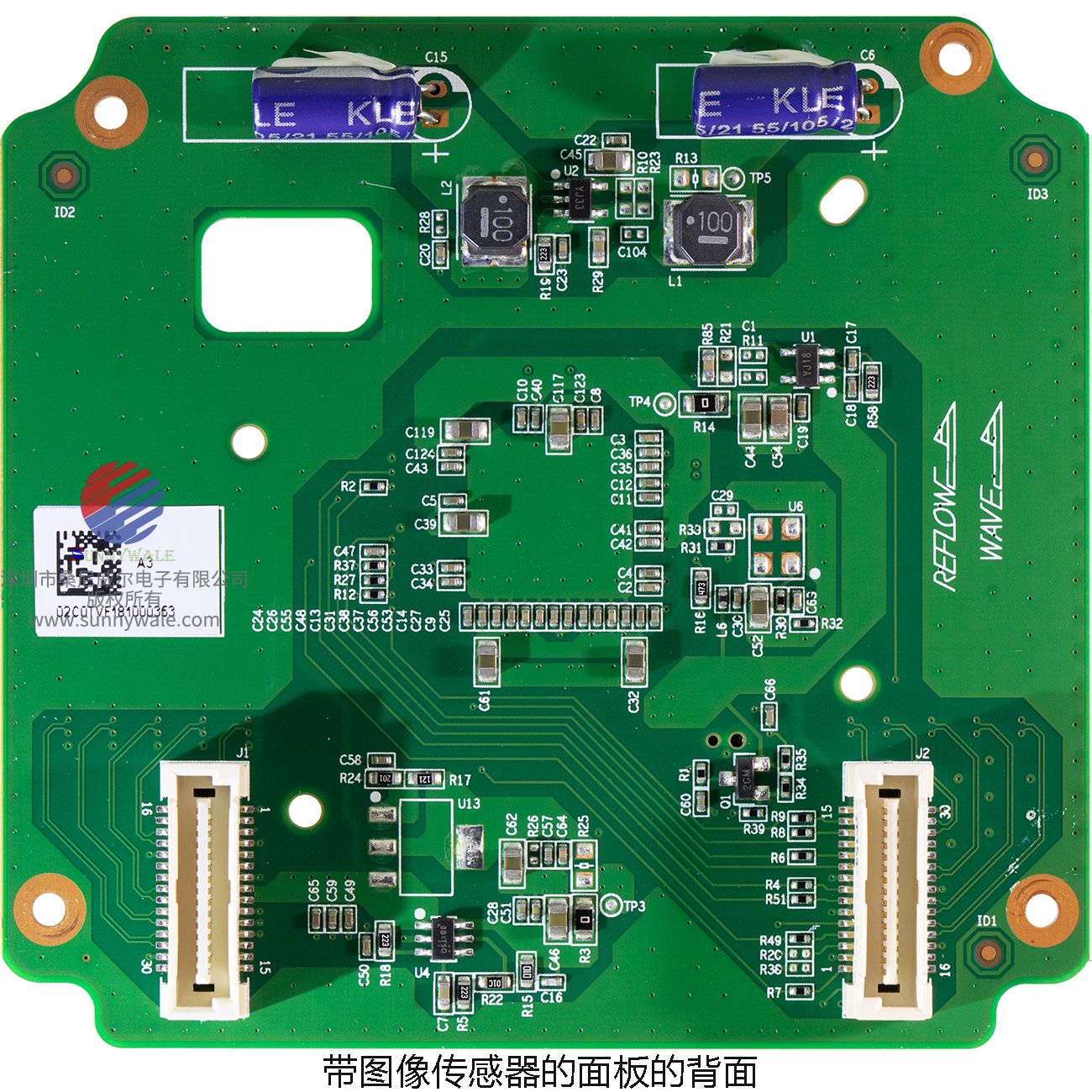

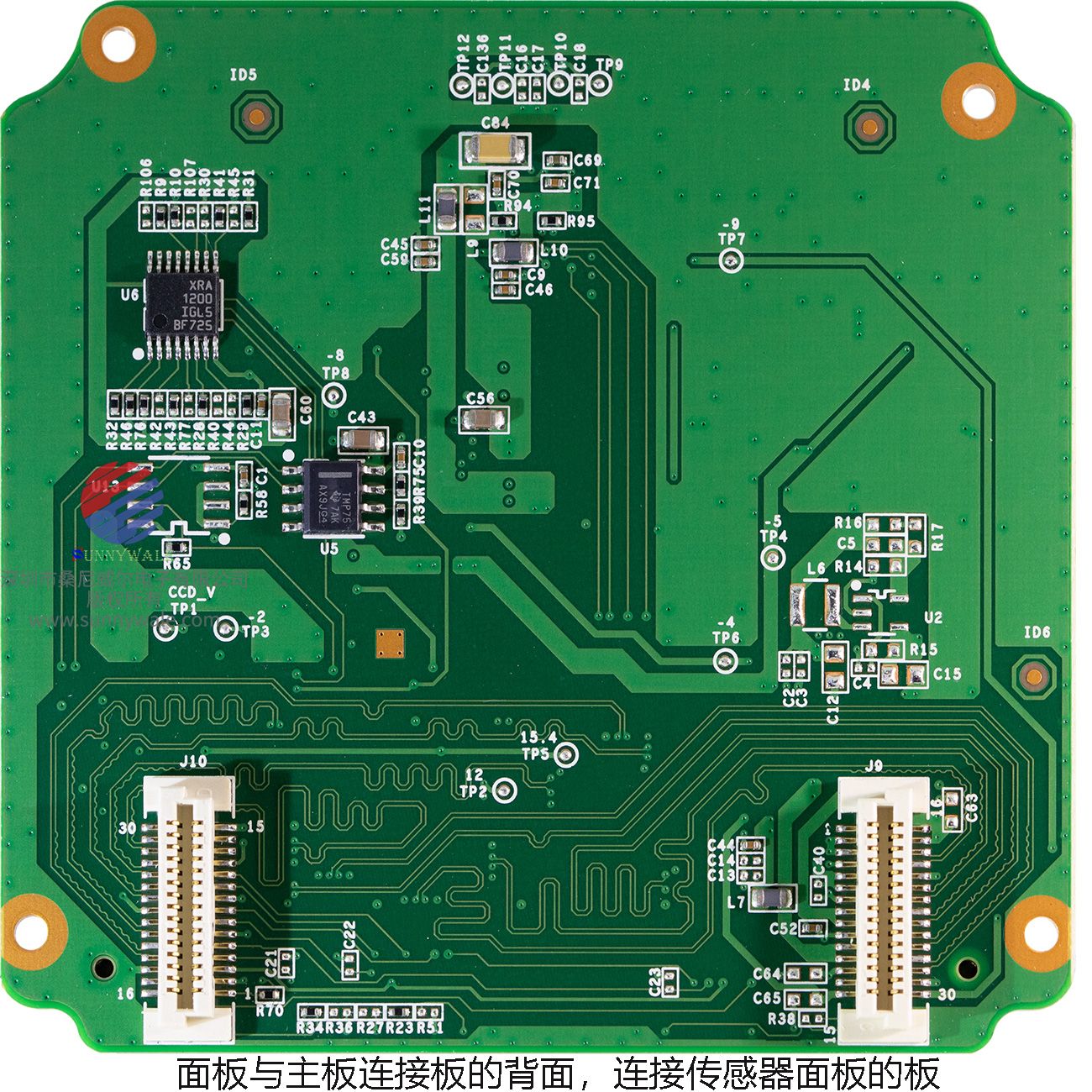

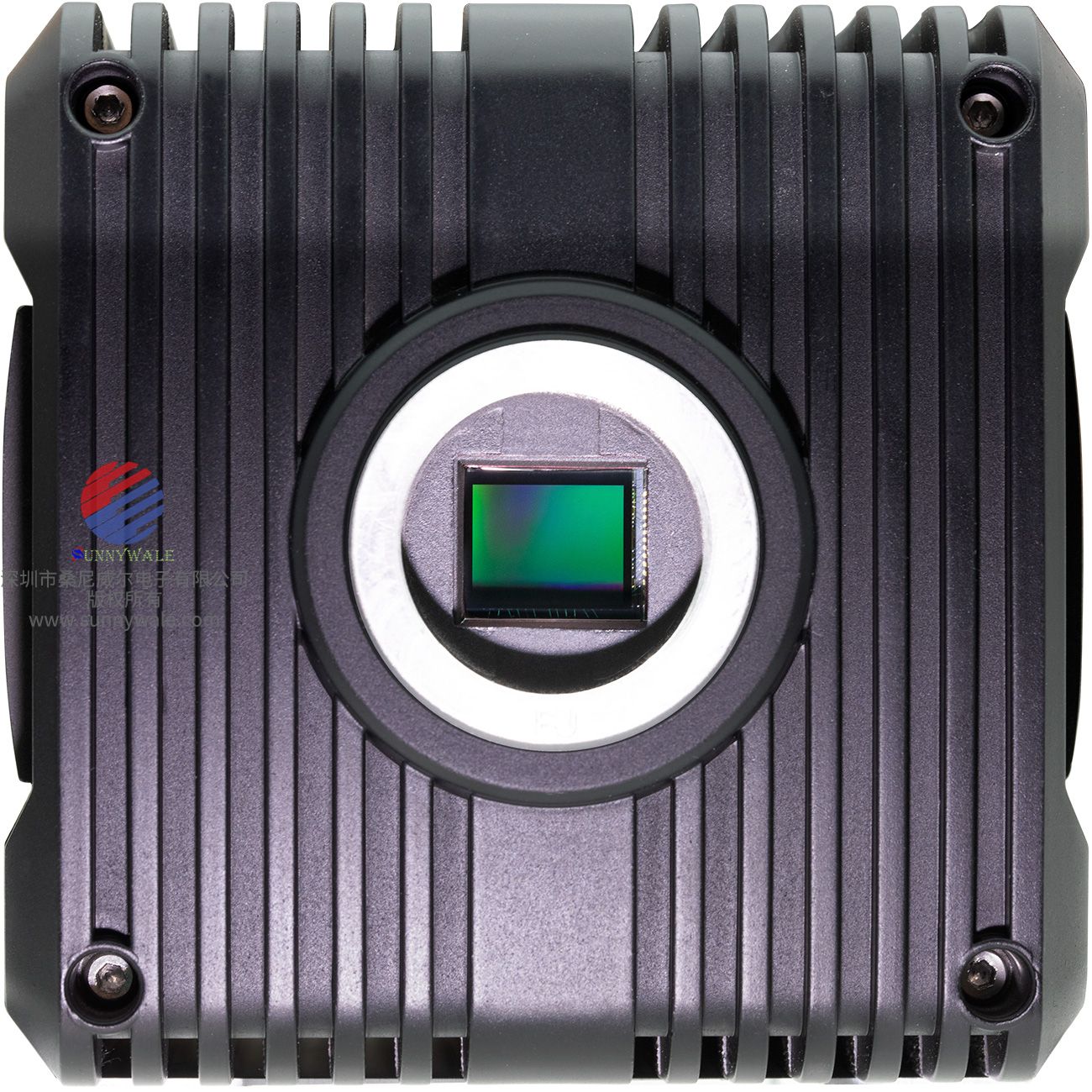

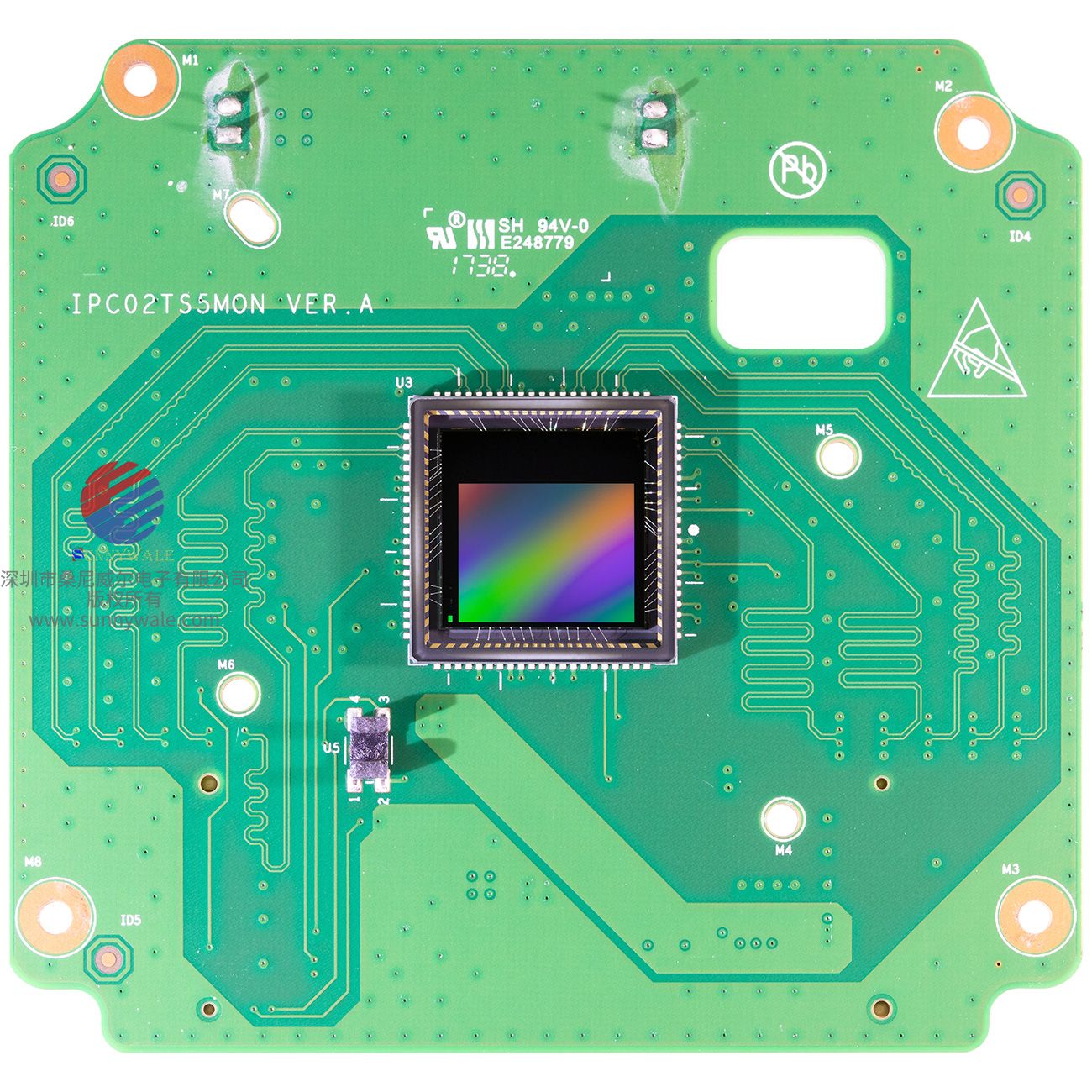

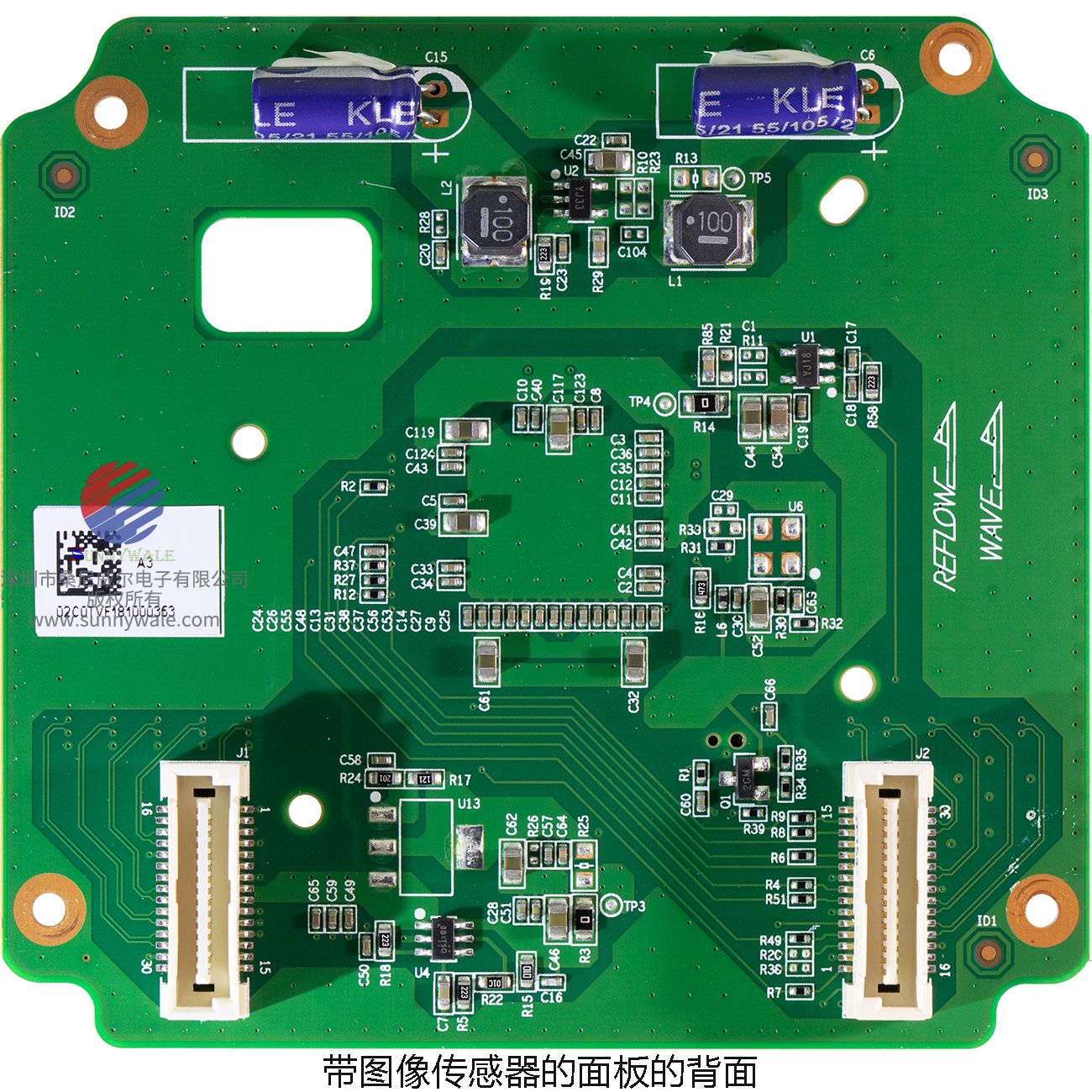

PYTHON5000 传感器面板正反面(上下图)

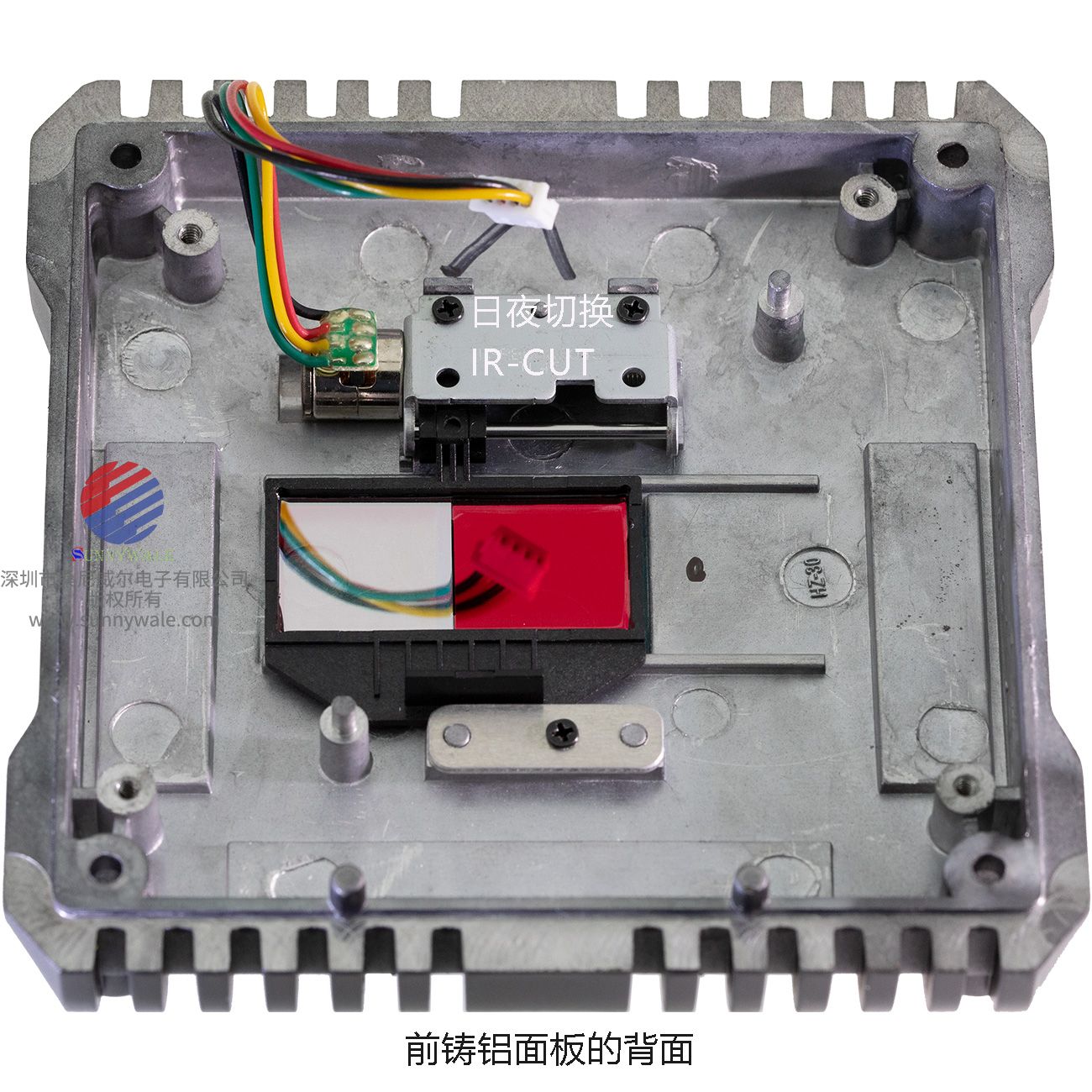

前铸铝面板zheng正面

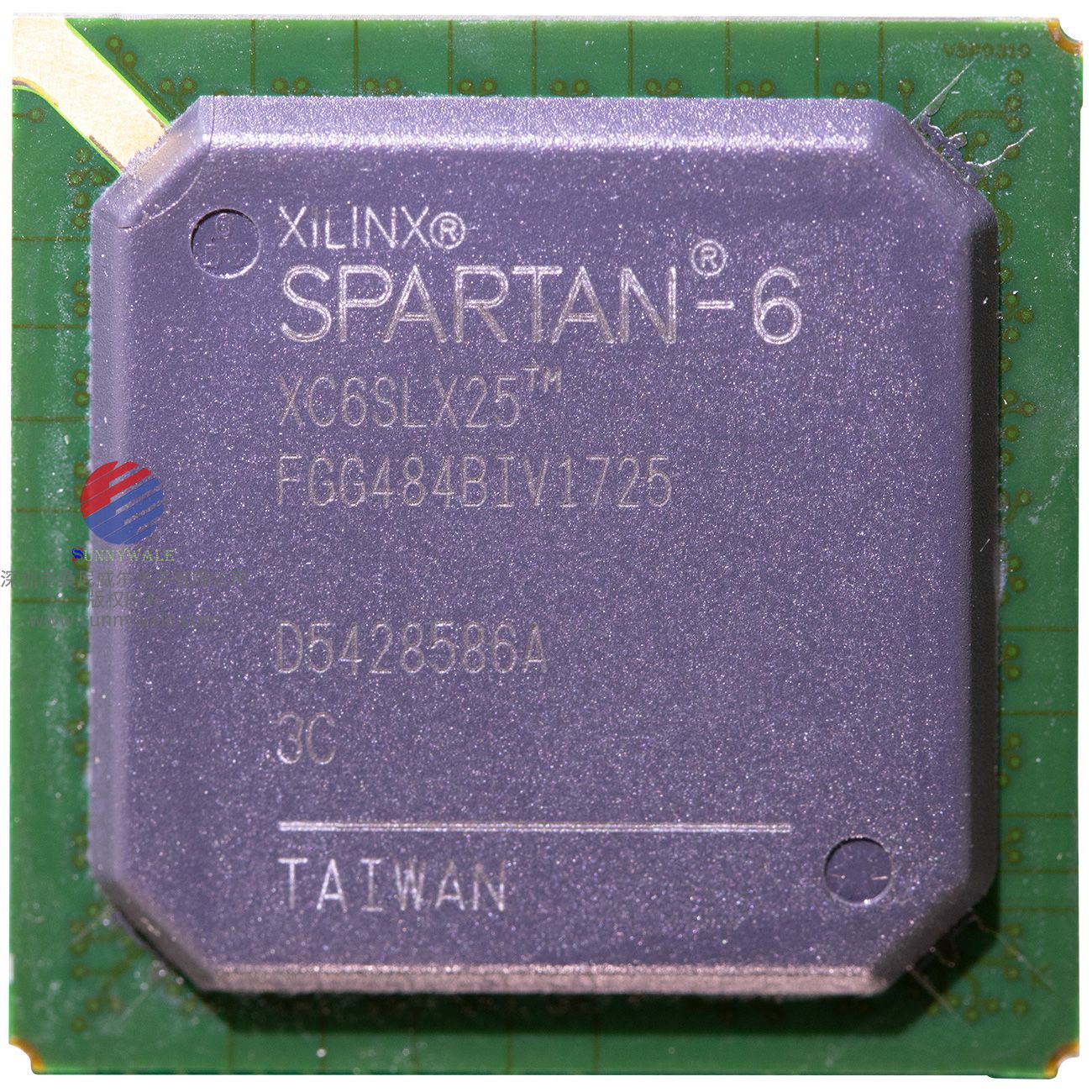

摄像机主要的板载IC:

Features

■ Data Output Options

⊙ P1-SN/SE/FN: 8 LVDS Data Channels

⊙ P3-SN/SE: 4 LVDS Data Channels

■ Size Options

⊙ PYTHON 5000: 2592 x 2048 Active Pixels, 1” Optical Format

■ 4.8 �m x 4.8 �m Low Noise Global Shutter Pixels with In-pixel CDS

■ Monochrome (SN), Color (SE) and NIR (FN)

■ Zero Row Overhead Time Mode Enabling Higher Frame Rate

■ Frame Rate at Full Resolution, 8 LVDS Data Channels (P1-SN/SE/FN only)

⊙ 100/85 frames per second @ 5 MP (Zero ROT/Non-Zero ROT)

⊙ 255/200 frames per second @ Full HD (Zero ROT/Non-Zero ROT)

■ On-chip 10-bit Analog-to-Digital Converter (ADC)

■ Eight/Four/Two/One LVDS High Speed Serial Outputs

■ Random Programmable Region of Interest (ROI) Readout

■ Serial Peripheral Interface (SPI)

■ Automatic Exposure Control (AEC)

■ Phase Locked Loop (PLL)

■ Dual Power Supply (3.3 V and 1.8 V)

■ -40°C to +85°C Operational Temperature Range

■ 84-pin LCC and 128 pad LGA

■ Power Dissipation

⊙ 1.45 W (P1-SN/SE/FN, 8 LVDS, NZROT)

⊙ 915 mW (P1-SN/SE/FN, P3-SN/SE, 4 LVDS, NZROT)

⊙ 520 mW (P1-SN/SE/FN, P3-SN/SE, 2 LVDS, NZROT)

⊙ 370 mW (P1-SN/SE/FN, P3-SN/SE, 1 LVDS, NZROT)

■ These Devices are Pb-Free and are RoHS Compliant

Applications

■ Machine Vision

■ Motion Monitoring

■ Security

■ Intelligent Traffic Systems (ITS)

Description

The PYTHON 2000 and PYTHON 5000 image sensors utilize high sensitivity 4.8 �m x 4.8 �m pixels that support

low noise “pipelined” and “triggered” global shutter readout modes. The sensors support correlated double sampling (CDS) readout, reducing noise and increasing dynamic range.

The sensor has on-chip programmable gain amplifiers and 10-bit A/D converters. The integration time and gain

parameters can be reconfigured without any visible image artifact. Optionally the on-chip automatic exposure control

loop (AEC) controls these parameters dynamically. The image’s black level is either calibrated automatically or can

be adjusted by adding a user programmable offset. A high level of programmability using a four wire serial peripheral interface enables the user to read out specific regions of interest. Up to sixteen regions can be

programmed, achieving even higher frame rates.

The image data interface of the P1?SN/SE/FN devices consists of eight LVDS lanes, facilitating frame rates up to

100 frames per second in Zero ROT mode for the PYTHON 5000. Each channel runs at 720 Mbps. A separate synchronization channel containing payload information is provided to facilitate the image reconstruction at the

receiving end.

-------------------------------------------------------------------------------------------------

1 High-Performance System-on-Chip (SoC)

1.1Features

● High-Performance DaVinci Video Processors

- Up to 1-GHz ARM Cortex?-A8 RISC Core

- Up to 750-MHz C674x VLIW DSP

- Up to 6000 MIPS and 4500 MFLOPS

- Fully Software-Compatible with C67x+, C64x+

● ARM Cortex-A8 Core

- ARMv7 Architecture

◆ In-Order, Dual-Issue, Superscalar Processor Core

◆ NeonTM Multimedia Architecture

◆ Supports Integer and Floating Point

◆ Jazelle? RCT Execution Environment

● ARM Cortex-A8 Memory Architecture

- 32KB of Instruction and Data Caches

- 256KB of L2 Cache

- 64KB of RAM, 48KB of Boot ROM

● TMS320C674x Floating-Point VLIW DSP Six ALU (32-/40-Bit) Functional Units

- 64 General-Purpose Registers (32-Bit)

- Six ALU (32-/40-Bit) Functional Units

◆ Supports 32-Bit Integer, SP (IEEE Single Precision/32-Bit) and DP (IEEE Double Precision/64-Bit) Floating Point

◆ Supports up to Four SP Adds Per Clock and Four DP Adds Every Two Clocks

◆ Supports up to Two Floating-Point (SP or DP)Approximate Reciprocal or Square Root Operations Per Cycle

- Two Multiply Functional Units

◆ Mixed-Precision IEEE Floating-Point Multiply Supported up to:

◎ 2 SP x SP →SP Per Clock

◎ 2 SP x SP → DP Every Two Clocks

◎ 2 SP x DP →DP Every Three Clocks

◎ 2 DP x DP →DP Every Four Clocks

◆ Fixed-Point Multiply Supports Two 32 x 32Multiplies, Four 16 x 16-Bit Multiplies Including Complex Multiplies, or Eight 8 x 8Bit Multiplies per Clock Cycle

● 128KB of On-Chip Memory Controller (OCMC)RAM

● Imaging Subsystem (ISS)

- Camera Sensor Connection

◆ Parallel Connection for Raw (up to 16-Bit) and BT.656 or BT.1120 (8- and 16-Bit)

◆ CSI2 Serial Connection

- Image Sensor Interface (ISIF) for Handling Image and Video Data From the Camera Sensor

- Image Pipe Interface (IPIPEIF) for Image and Video Data Connection Between Camera Sensor, ISIF, IPIPE, and DRA

- MImage Pipe (IPIPE) for Real-Time Image and Video Processing

- Resizer

◆ Resizing Image and Video From 1/16x to 8x

◆ Generating Two Different Resizing Outputs Concurrently

- Hardware 3A Engine (H3A) for Generating Key Statistics for 3A (AE, AWB, and AF) Control

● Face Detect Engine (FD)

- Hardware Face Detection for up to 35 Faces at OPP100

● Programmable High-Definition Video Image Coprocessing (HDVICP v2) Engine

- Encode, Decode, Transcode Operations

- H. 264, MPEG-2, VC-1, MPEG-4, SP/ASP, JPEG/MJPEG

● Media Controller

- Controls the HDVPSS and ISS

● Endianness

- ARM and DSP Instructions/Data - Little Endian

● HD Video Processing Subsystem (HDVPSS)

- One 165-MHz HD Video Capture Input

◆ One 16- or 24-Bit Input, Splittable into Dual8-Bit SD Capture Ports

- Two 165-MHz HD Video Display Outputs

◆ One 16-, 24-, or 30-Bit Output and One 16or 24-Bit Output

- Composite or S-Video Analog Output

- Macrovision? Support Available

- Digital HDMI 1.3 Transmitter With Integrated PHY

- Advanced Video Processing Features Such as Scan, Format, Rate Conversion

- Three Graphics Layers and Compositors

● Dual 32-Bit DDR2/DDR3 SDRAM Interfaces

- Supports up to DDR2-800 and DDR3-1066

- Up to Eight x 8 Devices Total 2GB of TotalAddress Space

- Dynamic Memory Manager (DMM)

--------------------------------------------page1-------------------------------------