Hi3531 H.264解码编码器,5路高清视频实时编码解码处理

2023-08-19 19:38:08

主芯片Hi3536RBCV100的功能:

功能结构:模拟集成电路

导电类型:单极型

集成度高低:位小规模集成电路

制作工艺:半导体集成电路

封装:BGA

主芯片Hi3531RFCV100的功能:

Hi3531是海思半导体针对多路D1和多路高清DVR、NVR产品应用开发的一款专业高端SOC芯片。高度集成和丰富的外围接口,在满足客户差异化产品功能、性能、图像质量要求的同时,可大大降低ebom成本。通过专用的视频级联技术,多片Hi3531间、多片Hi3531与Hi3532间级联可提供更强的编解码能力。

特点:

处理器:ARM Cortex A9双核@Max. 930MHz,

支持高达5路1080P实时多协议编解码,

智能视频分析:集成智能分析加速引擎,

支持智能运动侦测、周界防范、视频诊断等多种智能分析应用,

支持多种视频接口和集成丰富的外围接口,

SDK:提供基于Linux 2.6.38 SMP的开发包和H.264的高性能PC解码库,

封装:RoHS,EHS-FCBGA817封装。

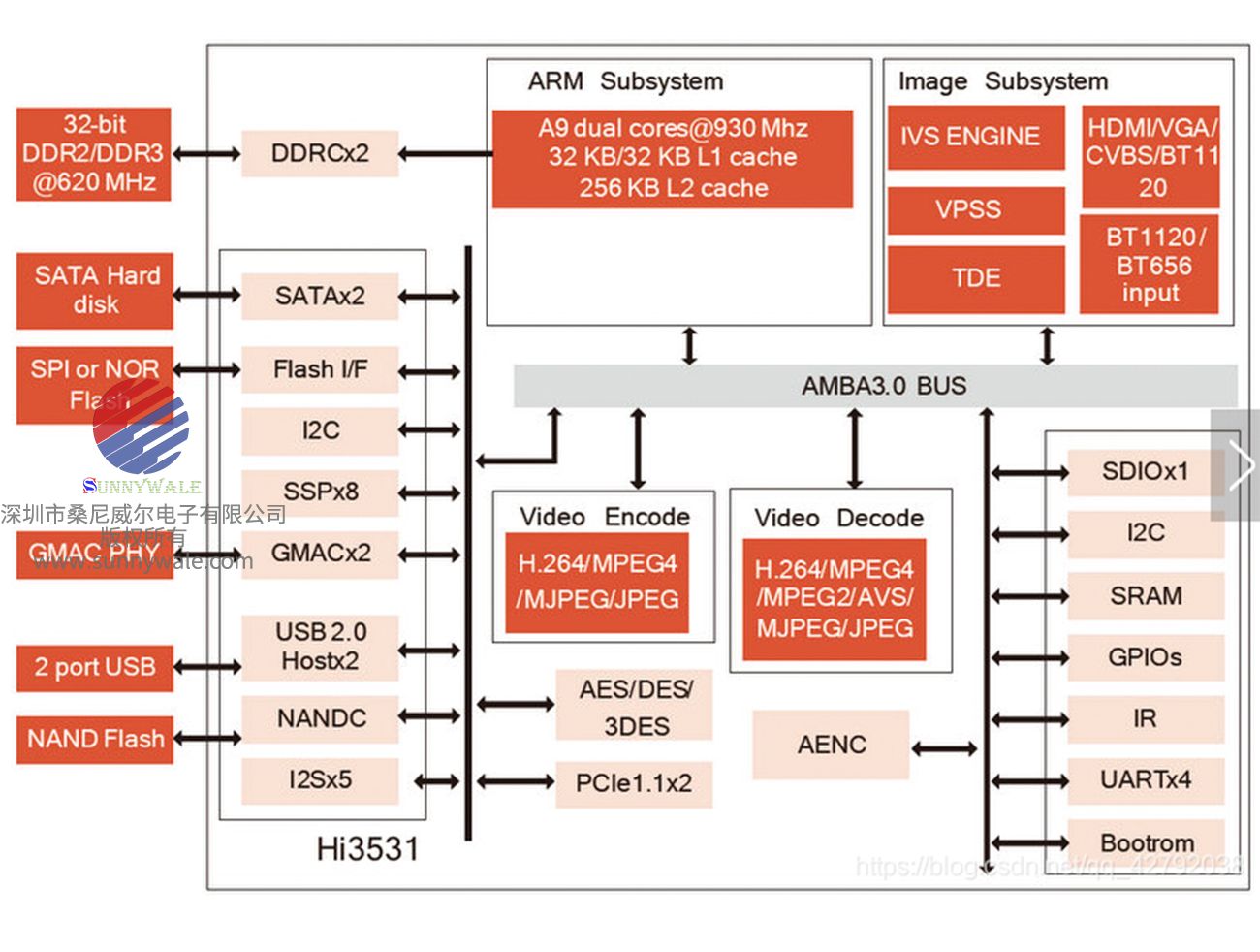

Hi3531功能框图:

————————————————

Hi3531为海思半导体针对多路D1和多路高清DVR、NVR产品,应用开发的一款专业高端SOC芯片。Hi3531内置强大的高性能双核A9处理器、高达5路1080P实时多协议编解码能力的引擎和专用TOE网络加速模块;集成优异的视频前后处理和编解码算法、结合多路高清显示输出能力。Hi3531高度集成和丰富的外围接口,在满足客户差异化产品功能、性能、图像质量要求的同时,可大大降低ebom成本。通过专用的视频级联技术,多片Hi3531间、多片Hi3531与Hi3532间级联可提供更强的编解码能力。

【Hi3531】

Hi3531高度集成和丰富的外围接口,在满足客户差异化产品功能、性能、图像质量要求的同时,可大大降低ebom成本。通过专用的视频级联技术,多片Hi3531间、多片Hi3531与Hi3532间级联可提供更强的编解码能力。

Hi3531 处理器 简介

Hi3531为海思半导体针对多路D1和多路高清DVR、NVR产品应用开发的一款专业高端SOC芯片。Hi3531 [2] 内置强大的高性能双核A9处理器、高达5路1080P实时多协议编解码能力的引擎和专用TOE网络加速模块,可轻松应对越来越高的高清应用和网络需求;集成优异的视频前后处理和编解码算法、结合多路高清显示输出能力,能充分满足客户产品的高质量图像体验。

海思3531芯片资料汇总

一、媒体处理平台(MPP) hi3531/3532 编码

二、视频缓存池:向媒体业务提供大块内存管理功能。

三、视频编码模块VENC支持以下协议编码:(1)H.264 (2)JPEG (3)MJPEG (4)MPEG-4

四、编码模块的输入源包括三类:

(1) 用户态读取图像文件向编码模块发送数据

(2) 视频输入(VIU)模块采集的图像经过视频处理子系统(VPSS)发送到编码模块

(3) 视频输入(VIU)模块采集的图像直接发送到编码模块

五、视频前处理单元VPSS(Video Process Sub-System)

(1) 支持对一幅输入图像进行统一处理,然后进行缩放输出。

(2) 一进五出(0~4)

(3) 一幅图像最多输出4种不同分辨率的预处理后图像。

0:主码流 1:辅码流 2:JPEG 3:预览

六、 典型的编码流程包括:

(1) 输入图像的接收

(2) 图像内容的遮挡和覆盖

(3) 图像的编码

(4) 码流的输入

七、编码通道:

完成图像转化为码流的功能,具体由码率控制器和编码器协同完成。

(1)码率控制器:提供了对编码参数的控制和调整,从而对输出码率进行控制。

(2) 编码器:只完成编码功能。

八、编码通道组:

指芯片启动一次,能够同时处理的编码通道的集合。

Hi3531/Hi3532编码通道组支持启动一次,仅编码一路主码流通道。

九、系统绑定:

通过数据接收者绑定数据源来建立两者之间的关联关系。绑定后,数据源生成的数据将自动发给接收者。

十、一些名词简写:

VI:视频输入 VO:视频输出

VPSS:视频处理 VDA:视频侦测分析

VENC:视频编码 AI:音频输入

VDEC:视频解码 AO:音频输出

十一、Hi3531解码器提供两种码流发送方式:

(1) 流式发送

(2) 按帧发送

十二、Hi3531解码器图像传输方式:

(1) 普通传输:完全按照H.264协议输出图像 速度慢

(2) 直接输出:收到下一帧码流,输出当前帧图像。 次之

(3) 按帧输出:收到当前帧码流,输出当前帧图像。 速度快

十三、 VI模块(视频输入)

(1) 实现的功能:将芯片外的视频数据,通过接口接收,存入到指定的内存区域。实现一路原始视频图像输入,两路视频图像输出功能。

(2) Hi3531芯片有4个BT.1120接口,每个BT.1120接口依次对应两个VI设备。

(3) Hi3531芯片有8个(4*2)VI设备端口(Dev0~Dev7),32个VI物理通道,2个级联扩展通道。

(4) 8个VI设备端口均支持2路D1复合模式,以及1路720P interleave模式。

十四、音频模块

Audio模块包括:

(1) 音频输入

(2) 音频输出

(3) 音频编码

(4) 音频解码