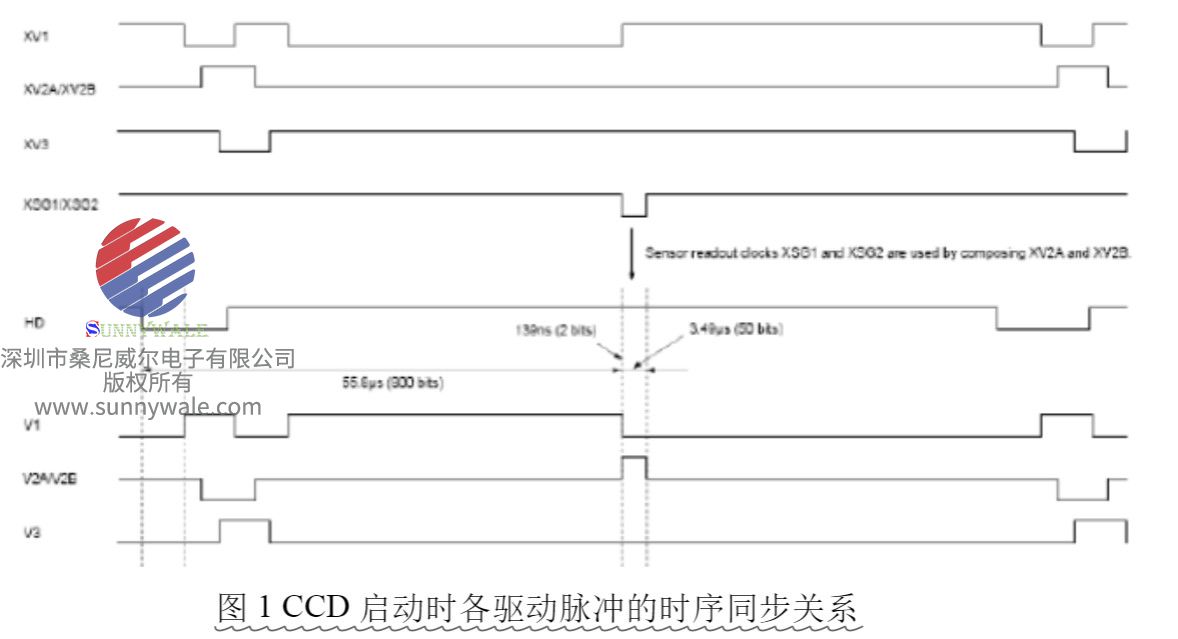

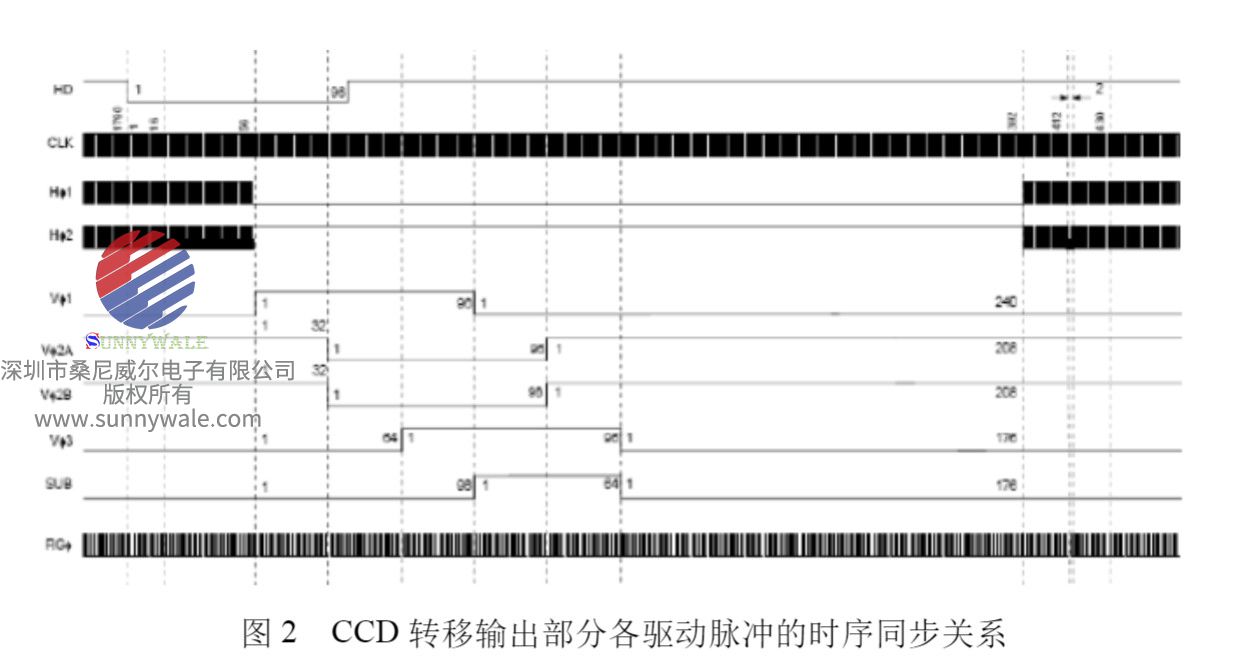

对图1 的理解: ICX205AL 的时序驱动需要外配一个 CXD1267AN 的芯片实现了该芯片的输入信号与输出信号的反相关系、叠加关系、以及信号电压幅值的大幅拉高, XV1, XV2A/XV2B, XV3是CXD1267AN的输入信号, V1,V2A/V2B,V3是相应的输出信号。HD的一个周期是启动的整个过程,以HD出现下降沿作为启动的开始, V1,V2A/V2B,V3各差32个脉冲周期(每个脉冲的标准周期是1/14.318M=69.8ns,这里的32个周期是通过图1上的比例量出来的,图2就标的明确了),由于有XSG1/XSG2的作用影响,在启动开始800个脉冲周期后,V2A/V2B出现了向上的突变,并维持50个脉冲周期。本次设计中,由于AD9923或者AD9927内含对CCD的V1,V2A/V2B,V3等驱动的管脚,因此CXD1267AN就不需要了,直接通过AD9927提供CCD驱动时序。CCD转移输出部分各驱动脉冲的时序同步关系如图2所示。

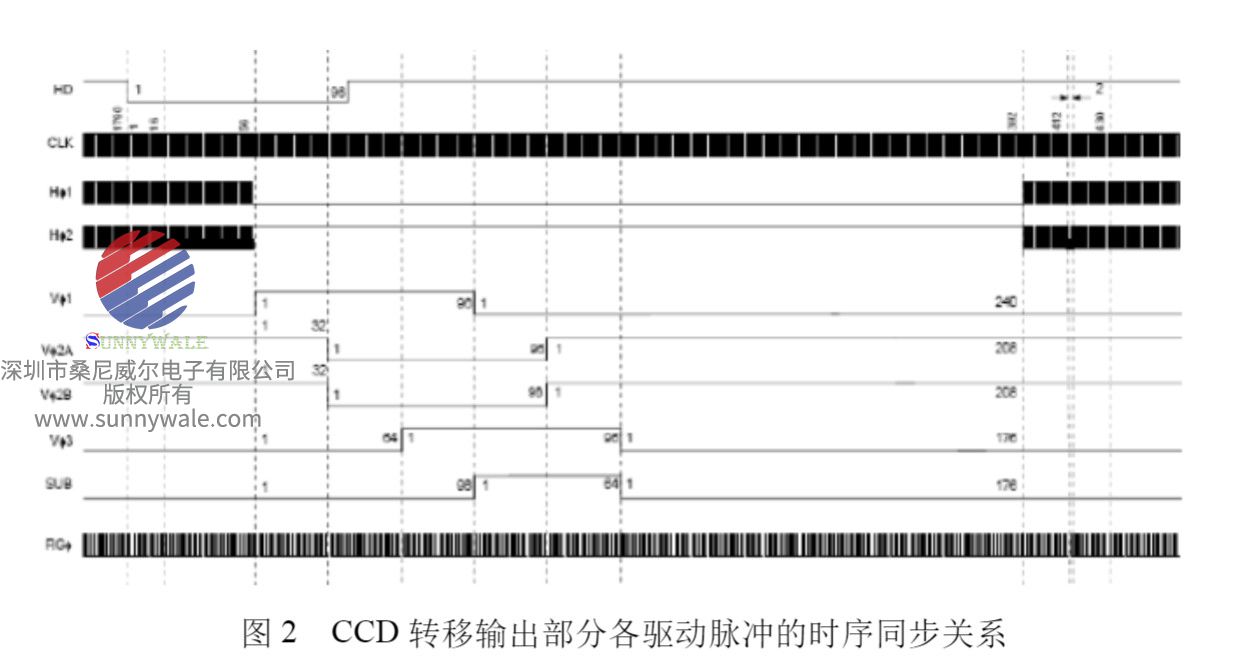

对图2 的理解:CCD转移输出的开始是以HD出现下降沿为标志的,这也正好接上了启动输出的信号,其他各信号同启动原理分析。一个转移周期包含1790个标准周期。编程时只要按照前面分析好的时序来编即可(注:时序的相位差通过软件延时即可实现)对启动周期编程:以hd产生下降沿为整个启动阶段的开始,输出信号有和时钟信号同频率的水平转移信号H1/H2 (在启动阶段sub信号不起作用),有相对低频的垂直转移信号xv1、xv2a/xv2b和xv3,他们的时序逻辑各差 32个时钟周期,还有 xsg1/xsg2信号,他们通过CXD1267AN的作用和xv2a/xv2b形成特征明显的三值信号 v2a/v2b,所以可以用v2a/v2b 来做观察启动周期的标志。一个 CCD的启动周期约是 104448 ns周期时间按照 ICX205AL所提供的时钟频率 14.318MHz 计算。对转移周期编程:各信号时序关系基本在图2标的很清楚了。编程时注意H1/H2的周期与标准周期相同且H信号中间有段时间是常值, RG信号分析下来在一个标准周期内是1: 3,不过就用标准周期clk 信号好像也行。一个CCD 的转移周期约是 124852 ns一个曝光周期包含一个启动周期和1068个转移周期。至此图像可以出来了。

ICX285/ICX205 DemoKit 性能与功能简介

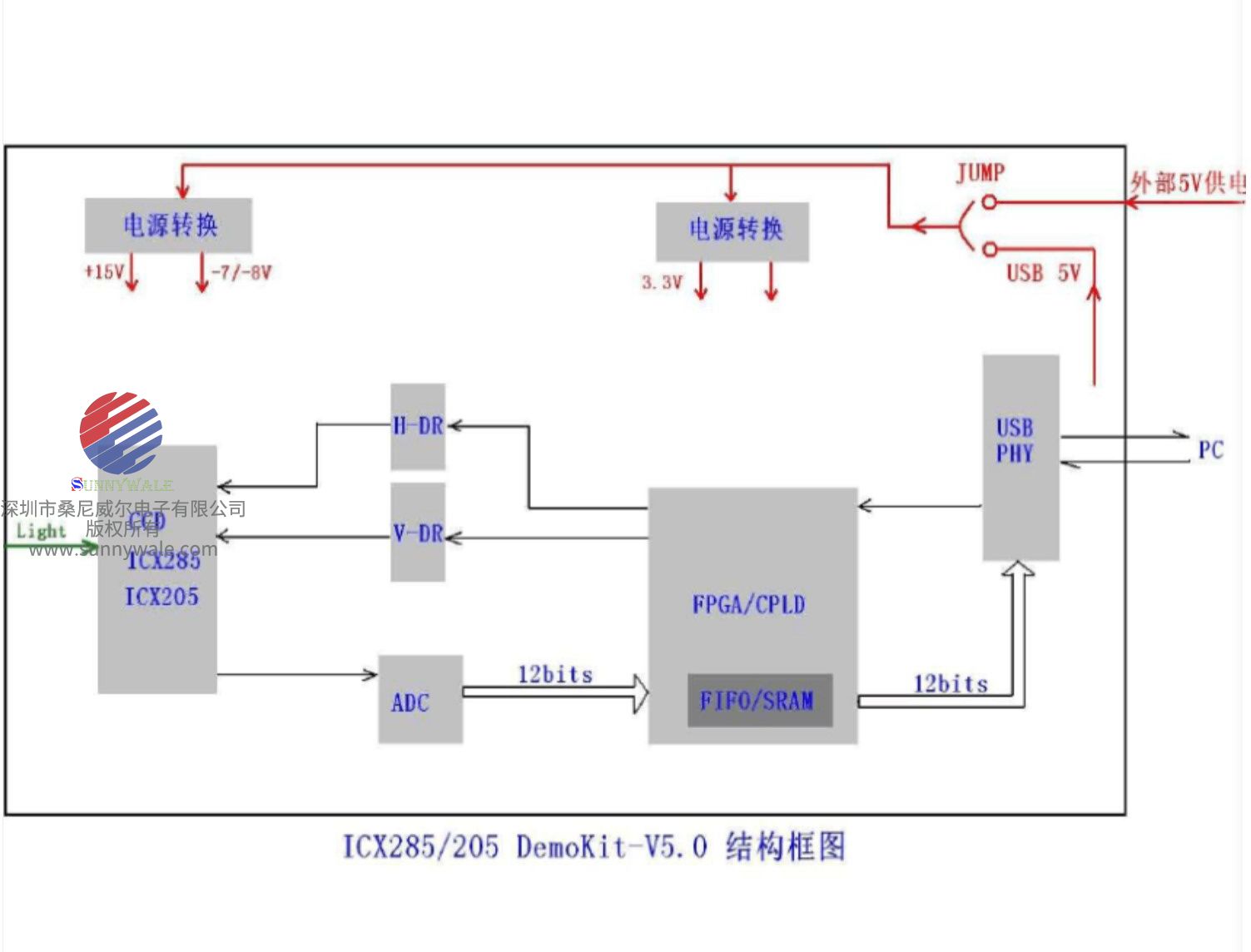

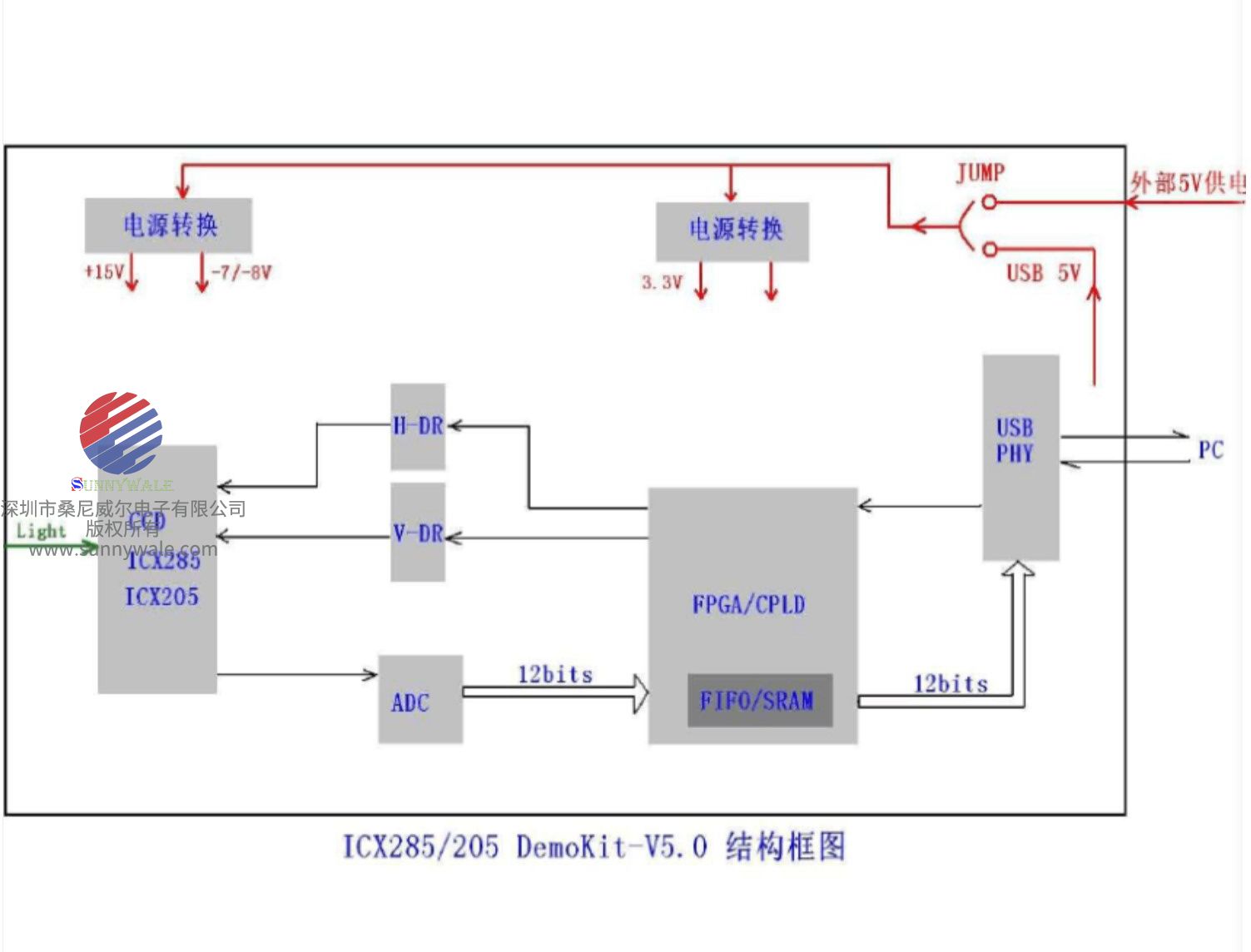

1.概述:ICX285/205 DemoKit-V5.0 CCD 成像组件可实现对ICX285和ICX205 两款CCD 的驱动并成像。该成像组件具有结构紧凑,性能可靠,功能扩展性好及升级改造空间大的诸多优点。其最少只需一根USB2.0专用电缆,即可实现电源供电、图像数据传输、参数设置等诸多功能。成像组件的曝光时间、增益、钳位等参数可通过开放性的用户端软件进行手动设置。CCD驱动方案采用通用的FPGA/CPLD产生驱动时序的方法,非常适合对CCD驱动电路的学习、科学研究型相机的设计、公司相关项目前期设计参考等等。

2.特性参数:

3.通电测试步骤:

(1).正确安装 USB 驱动 ezusb.sys;驱动安装方法可参考配套的驱动安装指导。

(2).选择成像组件的电源供电方式;可以采用USB 电缆供电,也可以选择外部独立5V供电。选择方法是:将电路板上的跳线 P1 跳至靠近 USB接口一端时,是选择的 USB 电缆供电。将电路板上的跳线P1 跳至靠近外部独立供电接口时,是选择的外部独立 5V供电。

(3).如果选择USB电缆供电方式,则跳过本步骤,执行步骤(4)。如果选择外部独立 5V供电,则应首先使用USB2.0 专用电缆,连接成像组件至 PC机。然后接通外部独立 5V 供电。

(4).如果选择USB电缆供电方式,请使用USB2.0专用电缆,连接成像组件至PC机。

(5).此时电路通电,程序启动,设备开始工作,PC机将识别成像组件设备。用户可通过“我的电脑->属性->硬件->设备管理器->通用串行总线控制器”来查看设备是否被正确识别。设备被正常识别时,“通用串行总线控制器”目录下将显示设备名"IOBOX X-Ray Device"或者"Cypress EZ-USB Sample Device"字样。此时设备处于待机状态,电路板上的绿色状态LED灯为固定频率的闪烁。

(6).双击打开配套的PC机图像采集软件,单击菜单栏的“开始采集”按钮,启动图像采集功能,此时在黑色图像显示区域将呈现实时图像画面。当前成像组件状态为采集传输状态,电路板上的绿色状态 LED灯为常亮。如果当前实时图像效果模糊,可通过调节镜头聚焦使图像清晰。如果当前实时图像效果较亮,可通过调节镜头光圈,使图像亮度降低。如果当前实时图像效果较暗,且光圈已经调到最大,可点击“参数设置”按钮,在弹出的对话框内适当设置增大曝光时间,或者设置增大增益,可使图像亮度提高。

(7).点击“停止显示”按钮,表示PC端用户软件停止接收数据,所显示的图像画面也停止刷新,但是成像组件还在向USB接口推送图像数据。此时成像组件仍未采集传输状态,电路板上的绿色状态LED 灯为常亮。

(8).点击“停止设备”按钮,表示PC端用户软件停止接收数据,所显示的图像画面也停止刷新,同时成像组件停止向USB接口推送图像数据。此时设备处于待机状态,电路板上的绿色状态 LED 灯为固定频率的闪烁。

(9).点击“保存”按钮,PC机将提示保存BMP格式文件存储路径,表示将要存储当前帧图像为.bmp 格式。

Notes:

(1).USB 支持热插拔功能,无论在采集还是待机状态,都可以随时拔掉 USB电缆。但是再次进行图像采集时,应保证首先连接USB2.0 专用电缆,然后再次打开PC机用户端软件。

(2).Line integration 也称为帧内曝光,指帧率不变的情况下改变曝光时间,曝光最大值即为一帧图像的传输时间。Exten integration 也称为长曝光,该模式下最短曝光时间为一帧传输的时间,曝光时间越长,帧率越低。

(3).如果在采集过程中出现“Can't open device!”字样,表示 USB 连接或者识别不正常。请检查电源供电是否正常。或者请关闭采集软件,重启 USB电缆后,再次采集。或者检查 USB 驱动安装是否正确。

4.功能介绍:

ICX285/205 DemoKit-V5.0 具有工业级相机和科学级相机的最基本功能,在满足图像实时传输的条件下,可实现曝光时间、增益、箝位等参数的任意调节。

成像组件实现了底层的CCD驱动,包括硬件电路的驱动设计和软件的驱动时序设计。将CCD成像电荷以15.625M的速度进行读出,经AD量化后,将数字图像传输至PC机,进行实时显示。

ICX285/205 DemoKit 开放了成像组件内部的曝光时间(Exposure)、 ADC的GAIN、及ADC 的 OFFSET 设置。

在该成像组件中,曝光时间分为长曝光(Extended Integration)和短曝光(LineIntegration)两种方式。其中短曝光是指,在帧率不变的条件下,进行的曝光时间的调节,曝光时间以CCD一行像素的读出时间为单位,软件设置范围是1~255。长曝光适应于长时间曝光的场合,在该模式下,曝光时间越长,帧率越低。长曝光的软件设置范围同为1~255。成像组件默认条件下,是短曝光模式,默认曝光时间是100*4Line时间。

增益GAIN 是 ADC的前置可编程增益放大器的增益设置。OFFSET 是 ADC的电压偏置设置。正确的设置GAIN和OFFSET,可以改变CCD的系统增益,使得CCD的输出信号范围与ADC 的量化范围相匹配,从而获得最好的动态范围。

默认情况下,GAIN值为6dB (最大 36dB), OFFSET 值为 128。软件设置范围均为0-255。

ICX285/205 DemoKit-V5.0成像组件配合上位机用户端软件,还可以实现抓拍并存储为.bmp文件的功能。另外,PC端用户软件具有较强扩展空间,用户可以根据自身需要,添加更加强大的扩展功能。例如,存储当前帧图像的原始数据,即RAW文件。或者添加实时录像功能。或者用户可以根据自身项目需要,添加合适的图像处理算法,实现目标识别,或其他功能。

5,设计思想描述:

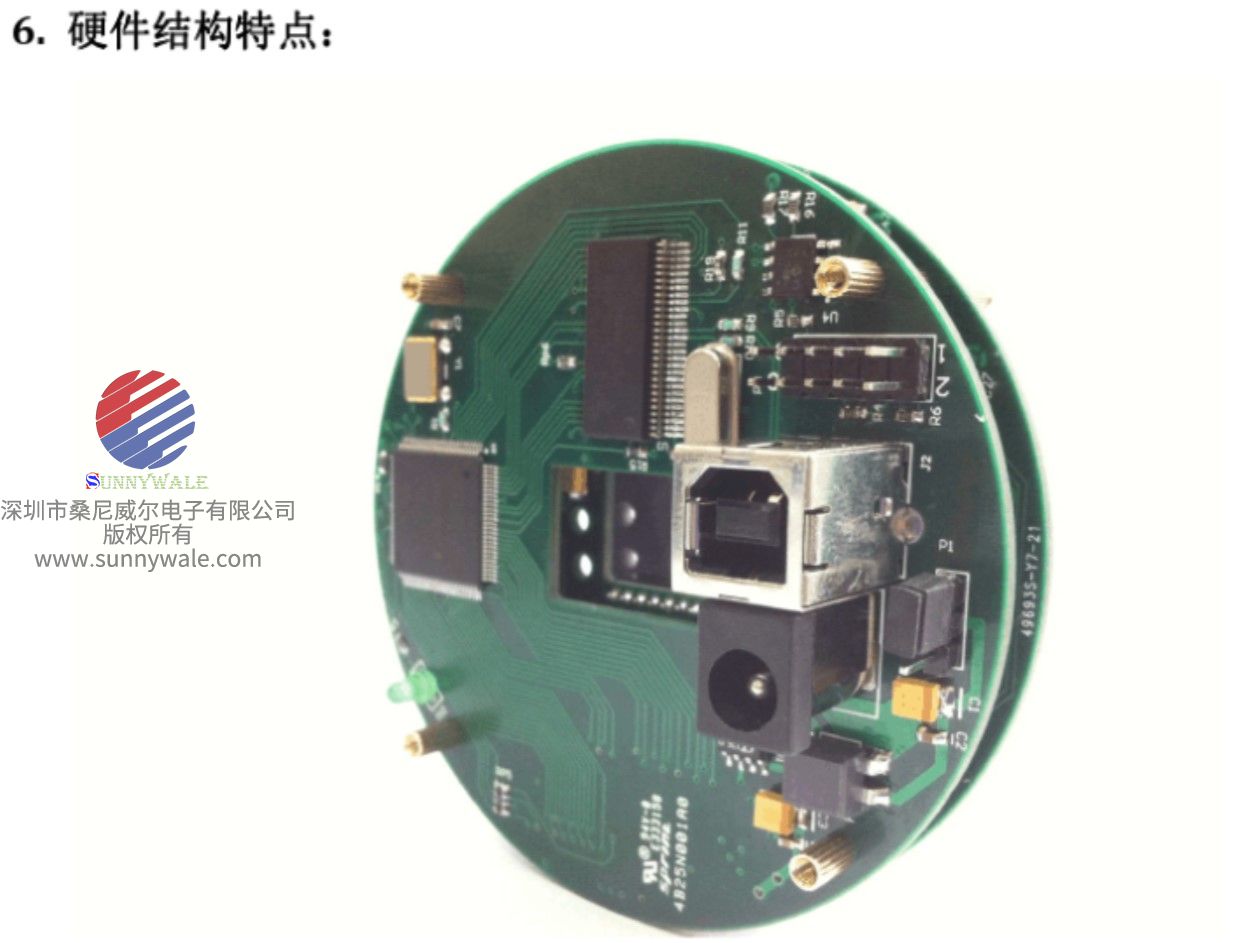

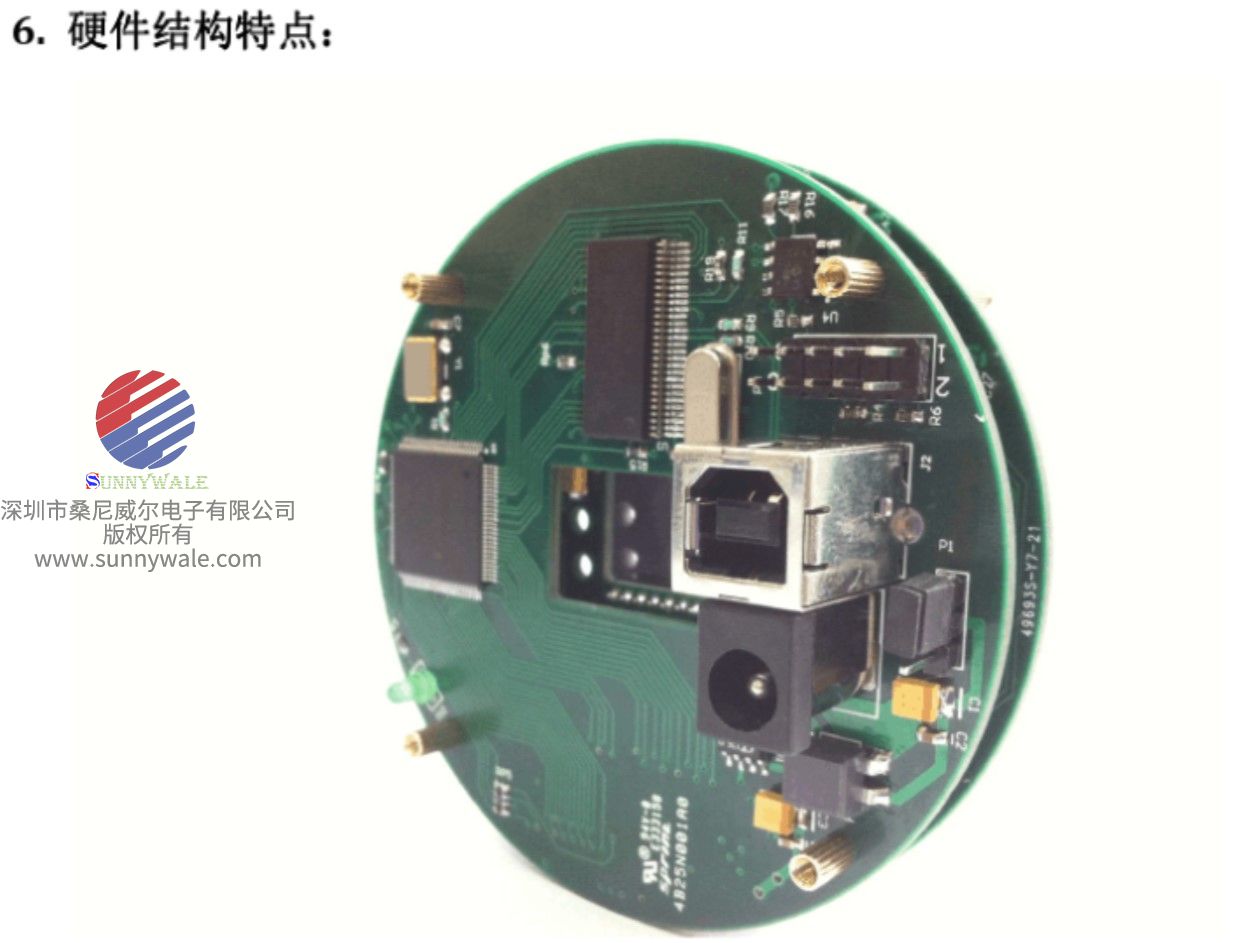

6,硬件结构特点:

ICX285/205 DemoKit-V5.0 采用两个电路板堆叠结构,每个电路板均设计为4层板,提高系统信号质量,提高抗干扰能力,提高系统可靠性及图像质量。电路分为CCD焦面电路板和FPGA时序接口板两部分。焦面电路板完成CCD的驱动和输出。FPGA时序接口板实现CCD驱动时序的产生及图像传输功能。其中,在两个四层板的中心(CCD下方)挖20mm*12mm的孔,方便扩展制冷接口,为长曝光下拍摄微光信号创造了较好的发展空间。

7.设计优点:ICX285/205 DemoKit-V5.0 成像组件经过多次改版, 目前方案设计已经趋于完美。实现了性能与结构的完美结合。设计中突出的优点主要体现在以下几个方面

(1).外部独立5V供电与USB电源可选。众所周知,不同的PC机USB端口的电源质量差异较大,有的端口电源纹波噪声极大,单靠外接设备自身的滤波,很难达到预期的电源效果。而CCD这类成像器件,对电源质量极为敏感,尽管成像组件在电源入口做了大量的滤波处理工作,但是为了满足更高图像质量的要求,所以特别添加了外部独立5V供电接口,可以使图像质量提高一个等级。

(2).硬件结构在CCD下方挖孔,为升级制冷电路提供了较好的解决方案。配合Peltiercooler和合适的外壳及导热结构,可实现对CCD的制冷,在长曝光或者采集微弱光信号方面,将得到非常完美的图像效果。

(3).硬件将驱动和时序部分分割设计,为小型化设计提供完美的解决方案。在理想情况下,CCD驱动电路的时序和驱动部分,如果放置在一块PCB上,效果是很理想的。但是在绝大多数应用场合,有各种各样的电路尺寸要求。该成像组件为用户提供了较完美的电路分割方法,在不大牺牲性能的情况下,最优化的减小设计尺寸。

(4).FPGA/CPLD驱动时序未使用任何IP core,完全用硬件描述语言实现底层时序驱动,这对于程序移植,升级改造来说,都是最理想化的。

(5).成像组件配合配套的用户端软件,可以实现工业相机及科学级相机的一些基本设置功能,即曝光时间、增益、箝位等。这些参数在实际应用中都是不可或缺的,而这些参数均使用手动任意设置,为用户提供了极大的方便性。

(6).成像组件提供了最基本的一系列功能,和CCD相机设计的典型设计思路,再配合各个模块配套的原始代码,可以方便的进行升级改造,升级改造空间巨大。非常适合初学者学习CCD的应用,和作为公司、研究所设计研发工业级、科学级CCD电路的前期设计参考。